配線がうねる? ルテニウムの弱点を克服する「型枠」の知恵

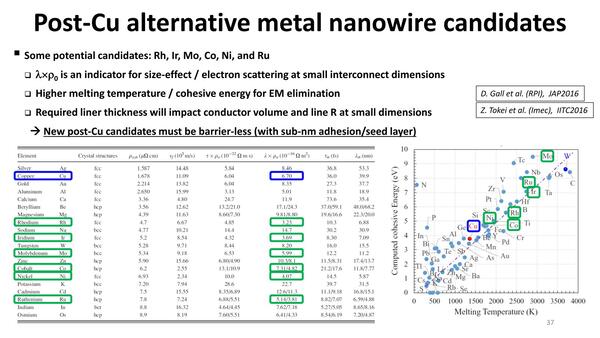

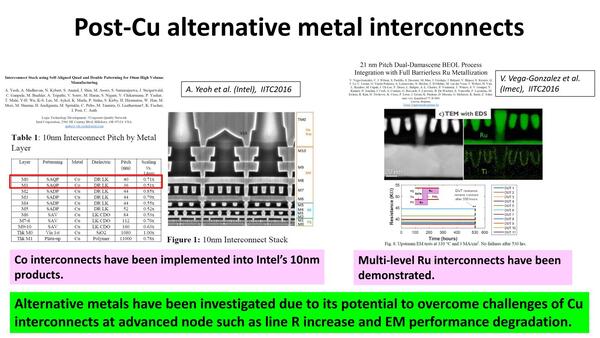

ではCuの代わりとして有望なのはなにか? 候補としてあがっているのはRh(ロジウム)/Ir(イリジウム)/Mo(モリブデン)/Co(コバルト)/Ni(ニッケル)/Ru(ルテニウム)といった材料になる。

ここで重要なのは、微細化の邪魔にならないように、(Cuのような)バリア層を必要としないこと、それとエレクトロマイグレーションに強いことだ。

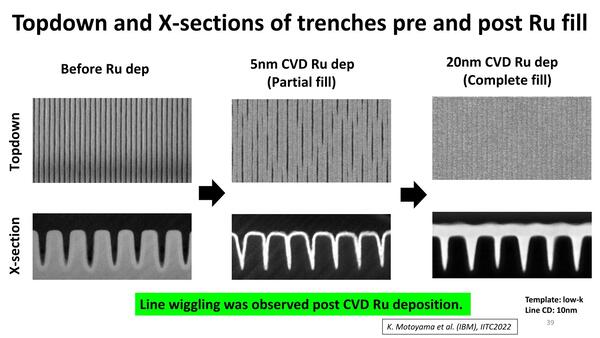

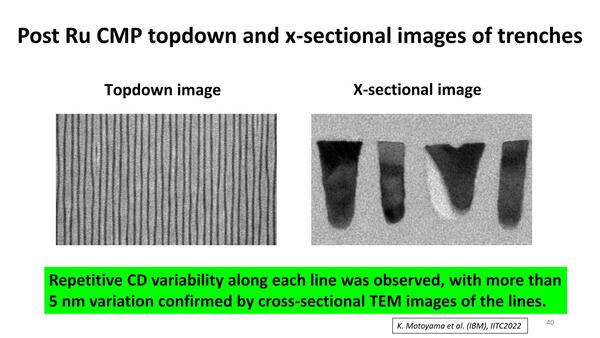

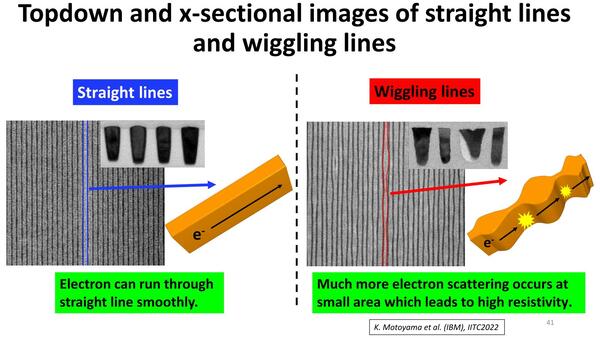

さて、インテルはRuが有望と説明したが、実際にはいろいろと問題がある。Ruを使う場合、Line Wigglingと呼ばれる現象が発生する。

配線の太さが不均一になるわけだが、これは配線の抵抗増の大きな要因になる。

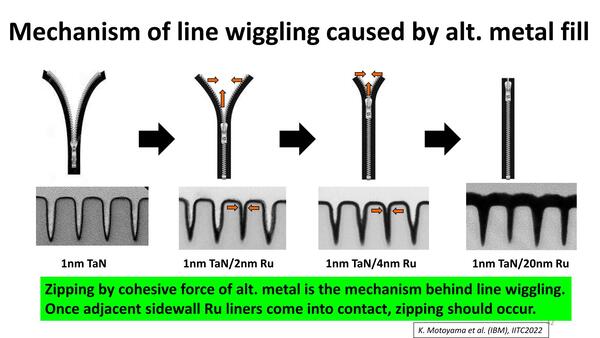

なぜこれが発生するのか、というメカニズムをファスナーに例えたのが下の画像である。Ruがお互いに引っ張り合うように作用し、結果として形が変形してしまうわけだ。

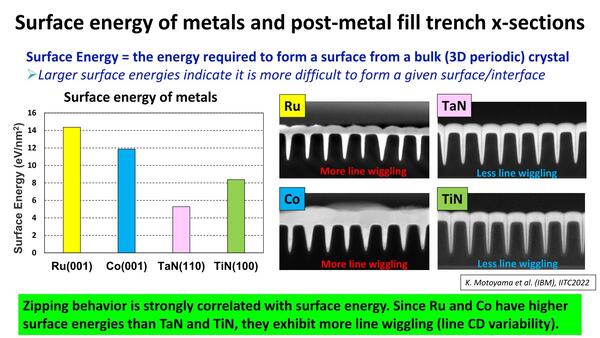

この現象はRuだけでなく、表面エネルギー(Surface Energy:物質の界面(表面)と内部で異なる分子のエネルギー状態であることに起因して発生する、界面あたりの過剰なエネルギー)が大きい材料ならば発生しやすくなる。

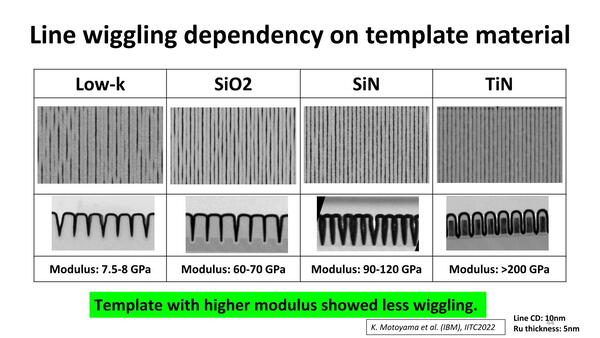

ちなみにLine Wigglingは、Template Material(型枠の材質)によっても変わってくる。要するにZippingが起きそうになっても(=Ru同士で引っ張り合いが発生しても)、型枠の形状が変わらなければLine Wigglingは発生しないからだ。

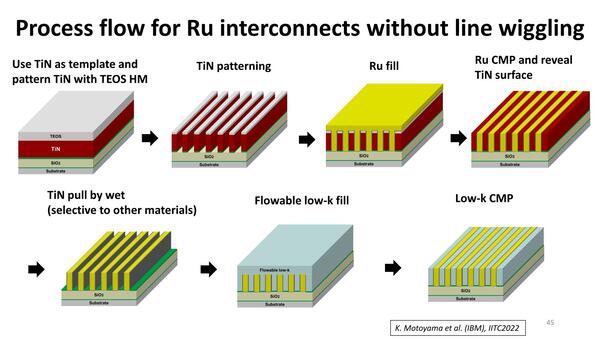

これを踏まえてのRuを利用しての配線構築方法が下の画像だ。つまりまずTiNで型枠を作り、Ruを埋め込んで配線層を構築。次いでCMPで上面を削り取りTiNを除去し、Low-K材料を埋めて完了だ。

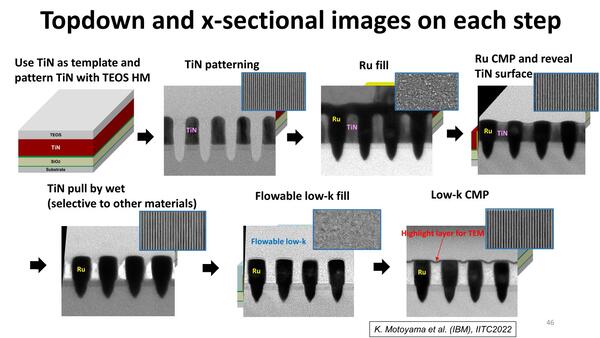

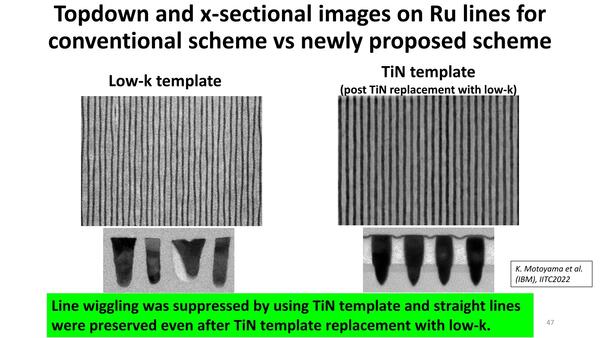

加工手順の各段階における断面写真が下の画像となる。そして作業完了したあとの配線の様子をLow-K材料を使った場合と比較したのがその下の画像だ。

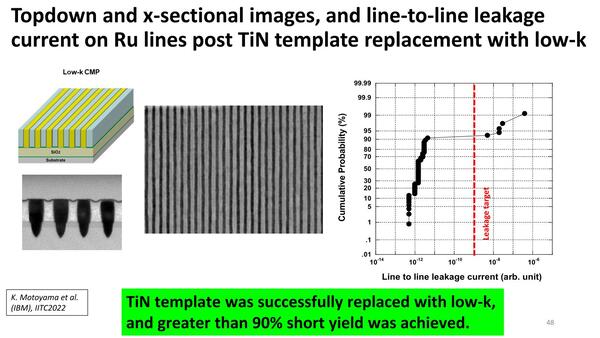

配線間のリーク電流の測定結果が下の画像で、90%の確率で目標値よりも3桁以上低いリーク電流を示しているのがわかる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ