前回はDRAMセルの話だったので、今回は配線の話をしていく。IEDM 2025のショートコースで、IBM Researchの本山幸一博士による"Advanced Interconnect Technologies for Cu Extension and Beyond"という講演があった。

講演そのものは、配線がアルミニウムから銅に移行を始めた1997年頃からの歴史を全部おさらいしており、復習の意味では有益な話なのだが、そこから説明を始めると長くなりすぎるので、後半の"Post-Cu alternative metal interconnects"の内容を中心にお伝えしよう。

トランジスタより配線が壁? 微細化を阻むCu(銅)の課題

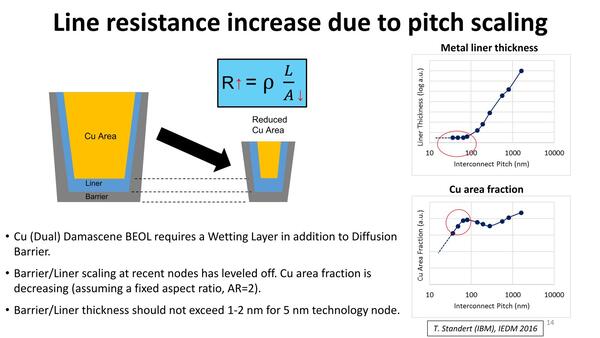

ポストCu世代に入る前に、Cu世代の問題について簡単にまとめておく。連載809回で、インテルがRu(ルテニウム)を配線に利用する話を書いたが、まずこの手前の話。配線ピッチを詰めていくと、配線層に占める銅の断面積がどんどん減り、抵抗が増えてエレクトロマイグレーション(材質に欠損が生じる現象)も起きやすくなる。

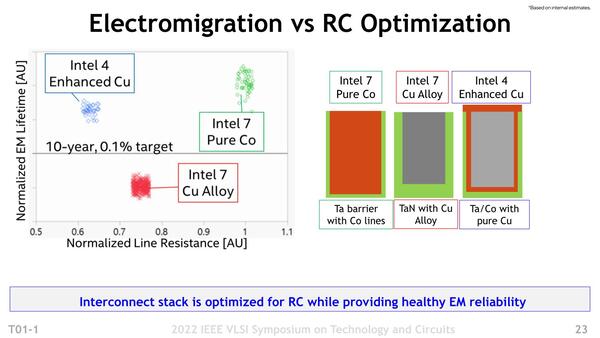

これをカバーするために、例えばインテルはTa/Co with pure Cu(銅配線の周囲をコバルトで覆い、その外側をタンタルでカバーする)という技法を編み出した。

IBMはTaとTaN(窒化タンタル)をバリア層に積層し、Cuの粒子サイズを大きくすることでエレクトロマイグレーション対策をするなど、いろいろ工夫をしているが、もうすでにプロセスの微細化はトランジスタそのものより配線の方がボトルネックになっている現状では、より微細化が求められることになり、もうCuのままで進めることは難しいと判断されている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ