ロードマップでわかる!当世プロセッサー事情 第860回

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新

2026年01月26日 12時00分更新

次世代AIプラットフォーム「Rubin」

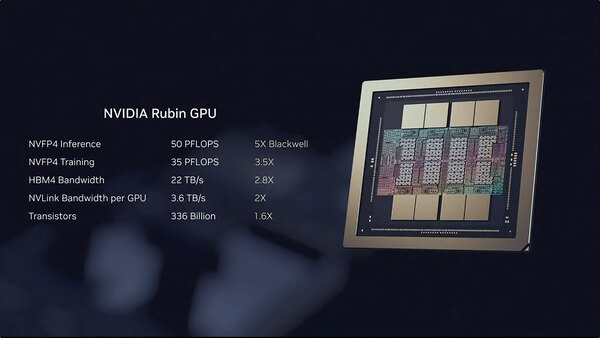

Veraに比べるとまだ謎が多く、情報が示されていないのがRubinである。昨年のGTCのスライドは72 GPUシステムとしての性能であり、今回はRubin単体の性能が示されたのが新しいといえば新しいのだが、まったく新しい情報と言えばトランジスタ数が3360億個であると示された程度だ。

Rubin単体の性能。GTCのスライドではFP8のトレーニングがFP4の3分の1の性能であるとされており、FP4のトレーニングは推論の3分の2の性能と推定されたが、今回ほぼこれに近い値(35PF:50PF=0.7倍)であることが確認できた

ただRubinに関しては、テクニカルブログの方でもう少し細かい話が出てきたので、こちらをメインに解説しよう。連載856回で、RubinのTensorコアの性能として以下の推定値を示した。

| Tensorコアの推定性能 | ||||||

|---|---|---|---|---|---|---|

| FP4 | 50PFlops | |||||

| FP8 | 25PFlops? | |||||

| FP16/BF16 | 12.5PFlops? | |||||

| FP32 | 6.3PFlops? | |||||

| FP64 | 225TFlops? | |||||

今回テクニカルブログでは以下の数字が示された。

| テクニカルブログで示された性能 | ||||||

|---|---|---|---|---|---|---|

| アーキテクチャー | Hopper | Blackwell | Rubin | |||

| FP32 Vector | 67TFlops | 80TFlops | 130TFlops | |||

| FP32 Tensor | 67TFlops | 227TFlops(*) | 400TFlops(*) | |||

| FP64 Vector | 34TFlops | 40TFlops | 33TFlops | |||

| FP64 Tensor | 67TFlops | 150TFlops(*) | 200TFlops(*) | |||

ここで(*)が付いているのはNVIDIAの説明が"Peak performance using Tensor Core-based emulation algorithms"なる脚注付きだからである。HopperまではTensorに関してもFP32/FP64用の専用演算器が搭載されていたのだが、Blackwell/Rubinに関しては低精度(おそらくFP16)用のユニットを複数パスをつなぐ形で処理しており、これにより精度と性能の両立を図っている、という説明であった。

ここで言っている複数パスというのは、例えば16bitの演算器を2つ並べて32bit幅の処理をできるようにする従来型のハードウェア的実装ではなく、例えば32bit幅ならそれを上位16bit/下位16bitに分割してそれぞれ別に計算し、後で1つにまとめる的な動作をしているように見える。

emulation algorithmsという言い方からすると、この動作はソフトウェア的に行なわれているようだ。要するにTensorコアはもう32bitのデータを直接的には扱わない構造である。ちなみに16bitが扱えるのか? もやや怪しい。というのはテクニカルブログにもFP16/BF16の性能が一切公開されていないからだ。ある意味8bit以下に最適化されているのかもしれない。

それともう1つ、FP4で推論が50PFlops、トレーニングが35PFlopsという数字になっていた。Blackwellではどちらも10PFlopsだったわけだが、Rubinで推論のみ性能が大きく上がっているのは、この数字がTransformer Engineを使った場合のものだからだそうだ。

このRubinに搭載されるTransformer Engineは第3世代に刷新されており、Blackwell世代と互換性を持つが、既存のコードは自動的に第3世代向けに最適化して実行する、と説明されている。逆に言えばTensorコアそのものの性能で言えばBlackwell世代からは3.5倍の向上に留まるわけだ。

現状まだRubin世代の詳細、つまりSM(ストリーミング・マルチプロセッサー)数や全体の構造、第3世代Transformer Engineの詳細などは明らかにされていないが、とりあえず性能的な部分に関してはある程度見えてきた格好である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ