ロードマップでわかる!当世プロセッサー事情 第847回

国産プロセッサーのPEZY-SC4sが消費電力わずか212Wで高効率99.2%を記録! 次世代省電力チップの決定版に王手

2025年10月27日 12時00分更新

PEZY-SC4sは年内にサンプル出荷、2026年に量産か

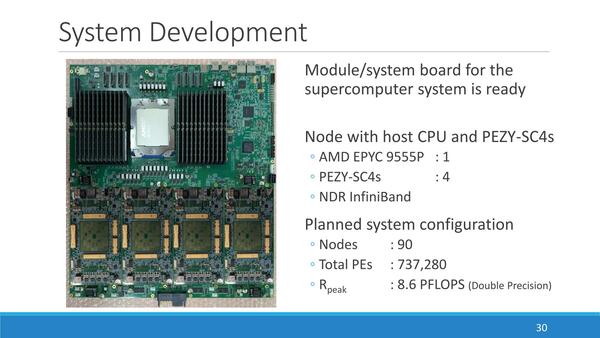

現時点ではまだPEZY-SC4sは発表されただけで出荷には至っていない(2026年の予定)が、すでに評価用ボードの準備は進んでおり、90ノード構成のシステムでのRpeakは8.6PFlopsとされている。

これがどの程度か?というと、今年6月のTOP500で言えば、例えば181位に入ったAlpha OneがRpeak 7.86PFlops/Rmax 7.62PFlopsになっており、効率(というかRmax)次第では180位前後に食い込む可能性がある。

90ノードということは、ラックあたり18ノード、5ラック構成だろうか? 冷却システム次第であって、このボードを見ると水冷配管は配慮していないように見えるので、実際にはラックあたり10~12ノードで、3U構成の空冷シャーシに収まる格好になるかもしれない。

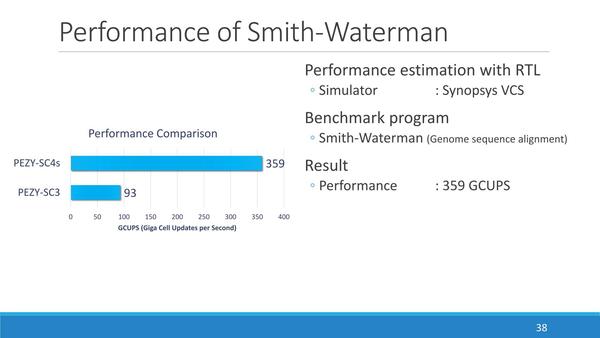

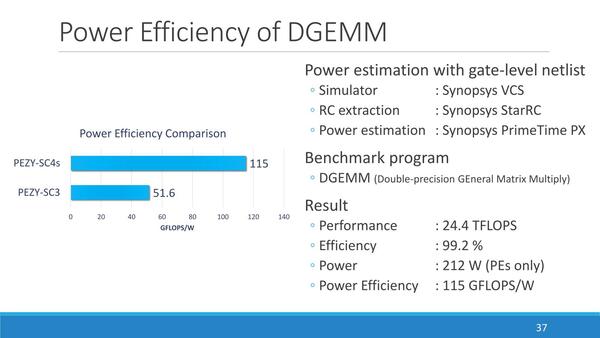

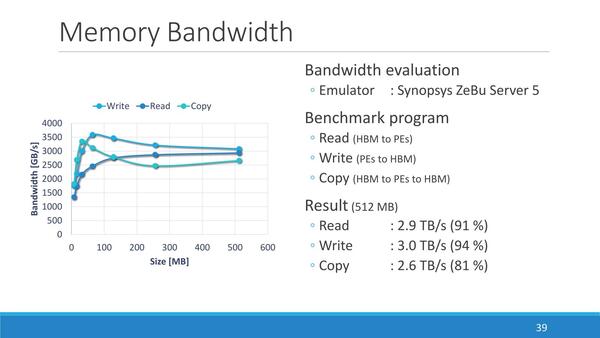

性能に関してはシミュレーションデータであるが、DGEMM、Smith-WatermanおよびMemory Bandwidthの結果が示されている。

DGEMMの効率はPEZY-SC3比で倍以上とされている。効率が99.2%、チップ(の中のPE)の消費電力は212Wとかなり省電力性に優れた結果に。逆に言えば絶対性能そのものはPEZY-SC3とそれほど変わらないかもしれない

PEとHBMの間の帯域は3TB/秒前後を確保しており、これは悪い数字ではないとは思うが、PEZY-SC4ではDDRのI/Fが省かれたので、HBMに入りきらないほどのデータを処理する場合に性能が大きく落ちそうなのが気になるところ

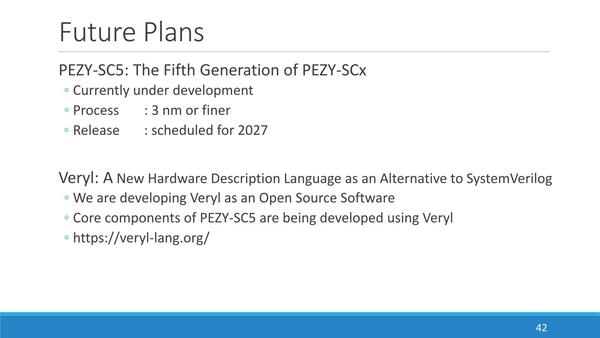

同社は今後のプランとしてPEZY-SC5を開発するとしているが、ベンチャーとしてはがんばっているものの2026年出荷では、競合はすでに3nmを使った製品を出してきているわけで、効率はともかく絶対性能という意味では結構厳しい戦いになるかと思われる。PEZY-SC5が登場するころには2nmチップが市場に出ている時期であり、効率性だけで戦えるのか、やや心配なところだ。

この連載の記事

-

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 - この連載の一覧へ