ロードマップでわかる!当世プロセッサー事情 第840回

Avicena Techが最新MicroLED光チップレット技術を公開! 2027年製品化に向けた新たな光インターコネクト戦略

2025年09月08日 12時00分更新

連載820回で、ISSCC 2025のフォーラムにおけるミシガン大学のEhsan Afshari教授が発表した、MicroLEDを利用したチップレット間接続の話をご紹介した。この時の内容はまだ研究レベルだったのだが、MicroLEDベースのチップレットの製品化を目指しているのがAvicena Techである。

そのAvicena、Hot Interconnectsではダイアモンド・スポンサーとなり、スポンサー枠で同社のChris Pfistner博士(VP, Sales&Marketing)が"Paradigm Shift in AI Scale Up Clusters using microLED based Interconnects"という短い講演を行ない、次いでテクニカルセッションでは同社創業者兼CTOのBardia Pezeshki博士が"Micro-LED data interconnect for scale-up networks with record energy efficiency"という講演を行なっている。そこでお二人の講演の内容をまとめて説明したい。

なお、Afshari教授は別にAvicena Techに参加しているわけではないが、2020年1月から2021年7月までの期間に"Low Power TIA and Drivers for Optical Interconnect"という研究でAvicena Techから助成金を受けており、まったく無関係でもない(おそらくこれが理由で、スライドの一部が被っている)。

スケールアップは、高効率・高密度・低コストを実現しつつ

10mほどの到達距離と低いBERを同時に実現できないといけない

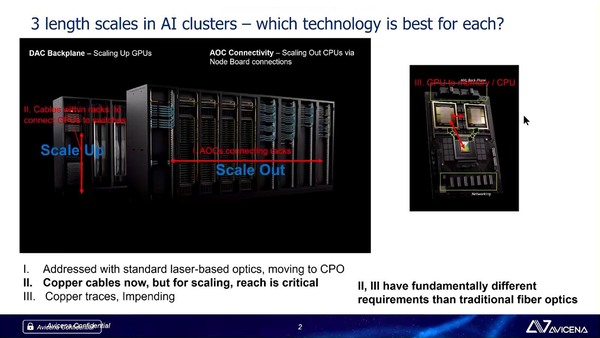

AIサーバーに代表されるシステムではネットワークの帯域が不足しているという話は、Avicena以外でも散々されているので省くとして、同社からするとこのネットワークはスケールアウト/スケールアップ、それとGPU to Memory/CPUの3種類で分けて考える必要があるとしている。

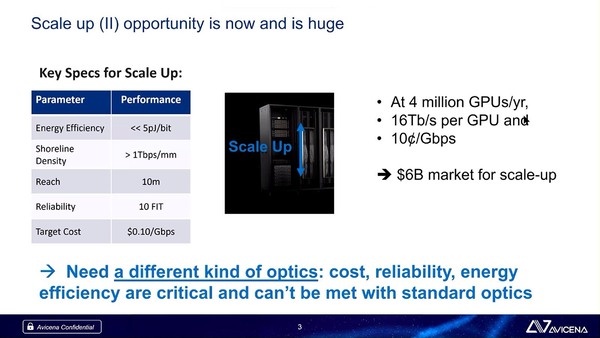

この中で同社が注目しているのはスケールアップの市場で、ここだけで60億ドルのTAM(Total Available Market)があるとしている。

スケールアップの要件。加えるなら、レイテンシーも結構な問題になるかと思われる。ただレイテンシーは配線距離に依存する(ラフに言って、光ファイバー1mあたり5nsほどの伝達時間がかかる)から、数値目標に入れにくいという事情もあるのだろう

ただしこのスケールアップに要求されるスペックは上の画像の左表に示されるように、高効率・高密度・低コストを実現しつつ、それでいて10mほどの到達距離と低いBER(10FIT=BERが10×10-8)を同時に実現できないといけないとする。これを実現するのには従来とは異なるなにか別のものが必要、というわけだ。

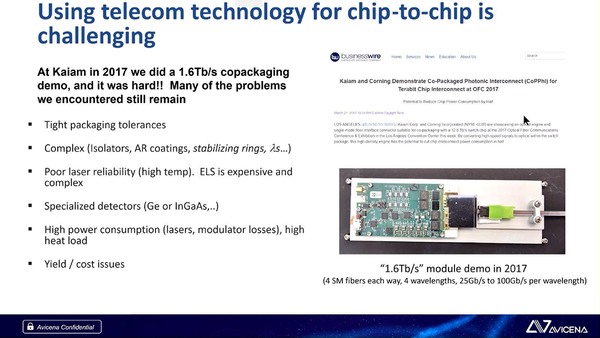

Pezeshki博士がAvicena Techの前に創業した会社がKaiam Corporationであり、2017年のOFCではCorningと組んで1.6Tbpsのチップ間インターコネクトの動作デモを行なっている。しかし、ここにもあるように技術的に困難な課題がいくつもあった。

FAU(右下写真の、黄緑のカバーがかかった部分)と基板の間に挟まる黒いモジュールがEICとPICを組み合わせたものだろうと想像される。余談だがこの写真、Afshari教授の時にも出てきていた

Kaiam自身は2009年に創業され、2013年にはスコットランドのGemfire Corpを買収してここでSiO(一酸化シリコン)ウェハーを利用した光学パッケージを製造したり、2017年にはCompound Photonics Groupのイングランドの製造拠点を買収したり(ただし同年8月にII-VI Corporationに再売却した)していたが、2018年にはそのスコットランドの製造拠点の生産能力を埋めるだけの注文が取れず、2019年には倒産している。おまけに倒産直前にはFinisarから特許侵害で訴えられるオマケつきである。

この時の経験で、従来型の光学コンポーネントではスケールアップ向けには向かないということがよくわかったようだ。そこで同社が着目したのはMicroLEDである。

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ