A14はNanosheet、A10はForksheetを採用か?

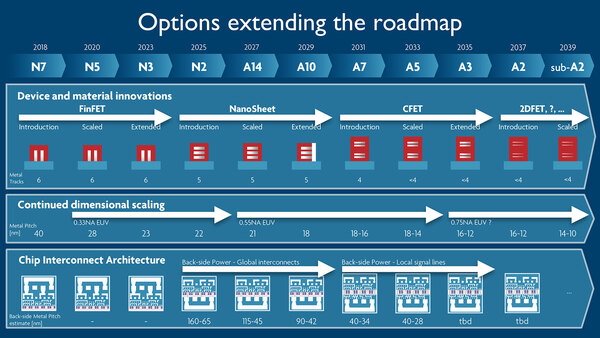

今回の発表はまだ研究段階のものではあるのだが、A14の次か、遅くてもその次くらいを見据えた、わりと現実的なものである。TSMCは2028年にA14プロセスの量産を開始予定となっているが、これはNanosheetないしScaled nanosheetの構成であり、Forksheetはその先だろう。

このロードマップ、2024年11月にimecが出した"Accelerating beyond-2nm innovation across the ecosystem"によれば、A14に続くA10までがGAAで、その先のA7がCFETになるとしている。A10がScaled Forksheetである可能性は低くないだろう。

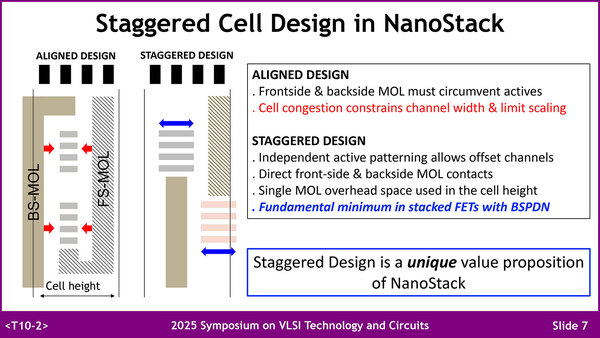

冒頭でIBMがCFETに関する論文を発表した話に触れたが、そのIBMが提案しているのはCFETをForksheetベースで構築するというものである。

左のAligned DesignはNFETとPFETをそのまま積層するものだが、右のStaggered Designは言ってみればForksheetを構築後に、中間部で切って上下にずらしたような構造である。利点はBSPDNの構築が容易なことである

こちらもまだ研究段階のものだし、IBMはそもそも量産設備を持たない(この研究結果がRapidusの将来のプロセスに使われるかどうかも怪しい)ので、あくまでも研究レベルの話ではあるが、TSMC的には(IBMのようなことをするかどうかはともかく)Forksheetにそれなりの可能性を見出しているらしい。さて実際にはどうなるだろうか?

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ