ロードマップでわかる!当世プロセッサー事情 第816回

シリコンインターポーザーを使わない限界の信号速度にチャレンジしたIBMのTelum II ISSCC 2025詳報

2025年03月24日 12時00分更新

Telum IIの話は一度連載790回で紹介している。順序から言えばz17相当になるのだが、z16はTelumとして発表され、その後継がTelum IIとなっている。8つのコアにDPUと推論アクセラレーターを搭載したチップであるが、そもそもこの写真はなんなのだ? というくらいにいろいろ情報が欠けていた発表であった。今回は多少不明点が解消された格好だ。

8つのチップで1枚のDrawerを構成するTelum II

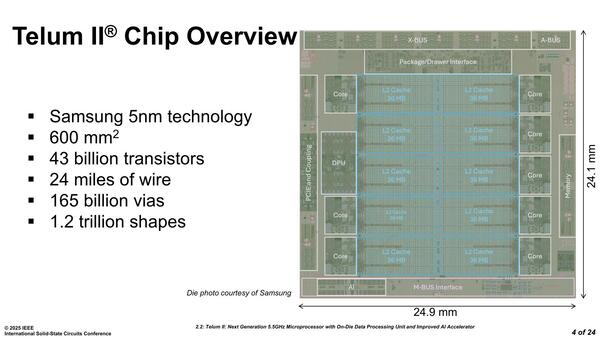

まず全体の構成だが、ダイサイズは600mm2で、430億トランジスタ。直接比較しても仕方がないが、TSMCのN5で製造されるZen 4のCCDが71mm2で65億トランジスタだから、トランジスタの密度は9155万個/mm2ほど、対してTelum IIは7167万個/mm2で、やや密度が低い印象を受ける。

もっともこのダイ写真を見ると、密度が濃い部分はCoreやAI、DPUなどの演算ユニットが入っている部分で、I/F部はほとんどが密度の低いPHYであることを考えると、こんなものかという感じもある。

そのTelum II、コア数は1チップあたり8つと少ないのだが、実際には8チップで1枚のDrawerを構成することになる。このDrawerが実際のプロセッサーの最小構成となるので、コア数は64という計算になる。

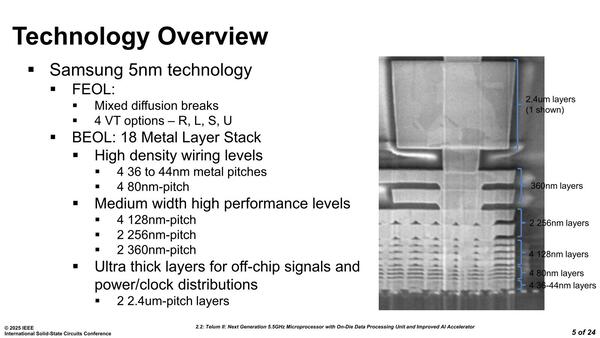

配線層は18層(16層+2 RDL)であると発表されている。これがSamsungの5nmの層数として標準的なものかどうかは確認できないが、例えばIntel 4は15層+RDLだったことを考えると、そう突飛な数字ではないと思われる。

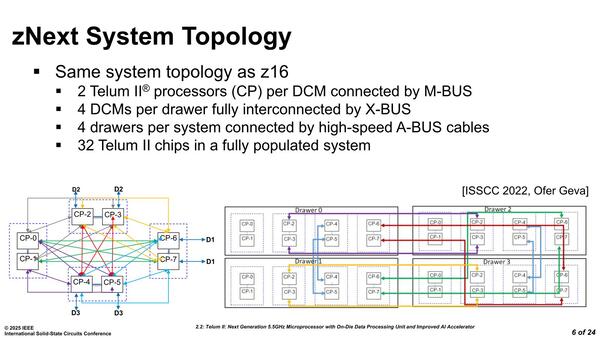

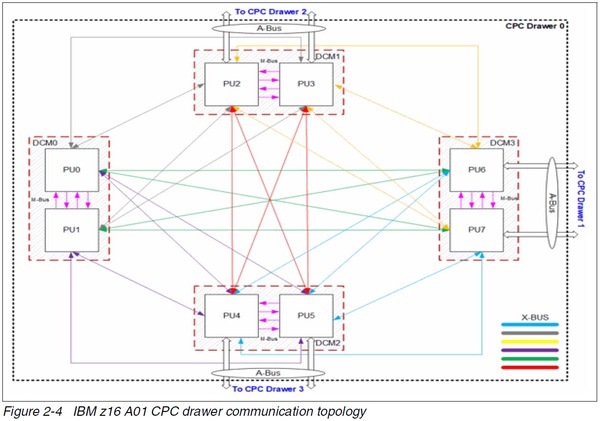

ところで最初の画像に戻るが、やけに多くのバスがあるのがわかる。以下がその概要であるが、これは先代のz16こと初代Telumも同じ構造であった。

- 個々のチップからはA-Bus/M-Bus/X-Busの3種類のバスが出る

- 2つのチップで1つのパッケージに収められる。IBM用語ではチップをCP(Central Processor)と呼び、このCPを2つ収めたパッケージをDCM(Dual Chip Module)と呼ぶ。このDCMの中で、2つのCPはM-Busを使って接続される

- 1枚のDrawerには4つのDCMが搭載される。このDCM同士の接続に利用されるのがX-Busである

- Drawer同士は、CP同士の接続の形で接続される。この際の接続に利用されるのがA-Busである。CP-0/CP-1のA-Busは未接続であり、Drawer同士の接続には使われない

このA-Bus/M-Bus/X-Bus、バスのプロトコルそのものがどうなっているのかの開示がないのでわからないが、おそらく物理的には以下のようになっているものと思われる。

| M-Bus | 2つのチップ間をパッケージ上で繋ぐので、速度を控えめにしてその分バス幅を増やした構造 |

|---|---|

| X-Bus | Drawer上でのDCM同士の接続になるので、M-Busよりはバス幅を減らし、その分信号速度を上げた構造 |

| A-Bus | Drawer間を跨ぐ接続になるので、配線そのものがシャーシの外に出ることになる。なので配線数を大幅に減らし、その分信号速度をギリギリまで上げた構造 |

こういう構成は珍しい。例えばAMDのMI300Cを例に取れば、1つのパッケージ内での接続はI/Oダイ同士をシリコン・インターポーザーで接続する形になっており、ここはTelum IIで言うところのM-Busに相当する。ただキャリアボード上にMI300Cを複数接続するのはインフィニティ・ファブリック経由になっており、これがTelum IIで言うところのX-Bus相当である。

ここまではいいのだが、キャリアボード同士の接続はAMDならPCI Express経由であり、スイッチを挟んでスケーラビリティを確保できる。さらに大規模な場合は、FrontierのようにPCI Expressの先にネットワークカードを装着し、相互をSlingshotなどでつなぐ形になる。これに対しTelum IIではA-BusでPoint-to-Pointの相互接続になっているあたりがあまり一般的ではない。

もっともこの構成では4 Drawerが最大になっている。ではもっと大規模なシステムはどうするか? というと、Coupling Expressと呼ばれるIBM独自のイーサネットベースのインターコネクトがあり、これで疎結合の形でシステム同士を接続することになっている。要するに通常なら1枚のキャリアボード(Telum IIで言うならDrawer)内部の接続に使われるのがローカルインターコネクトであるが、IBM的には4 Drawerまではローカルインターコネクトでつなぐという位置づけにあると考えた方が良さそうだ。

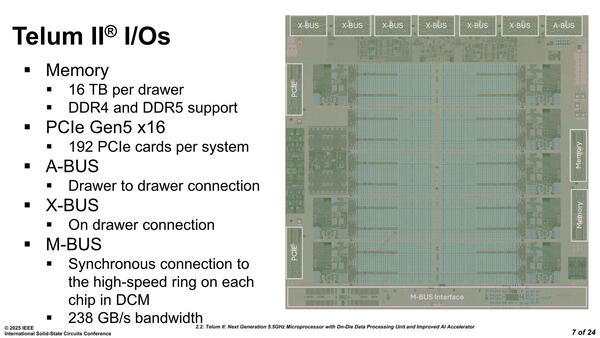

もう少しI/Oまわりの話を続けよう。Telum IIのI/Oが下の画像であるが、TelumではPCIe Gen4x16ないしPCIe Gen5x8がチップあたり2つだったのが2×PCIe Gen5x16になった。

Telum IIのI/O。メモリーは、Telumの時代からDDIMM(Differential DIMM)を利用しており、1つのDCMに16枚のDDIMMが接続できる構造になっている。Drawer全体で言えば64枚で、これで最大16TBという構成である

ちなみにそのTelumの場合1枚のDrawerに最大14枚、1システムで56枚のカードが装着可能だったのが、Telum IIでは最大192枚という壮絶な数に増えている。Drawerあたり48枚になる計算で、おそらくはPCIe Bifurcation(x16を2x8や4x4/8x2/16x1に分割できる)を組み合わせてこの数字になっている(か、Drawerの外にPCIe Switchを搭載したカード増設用のシャーシが用意されるかのどちらか)ものと思われる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ