当初は歩留まりが平均70%程度とかなり低い数値だったが

今ではかなり歩留まりを改善できた

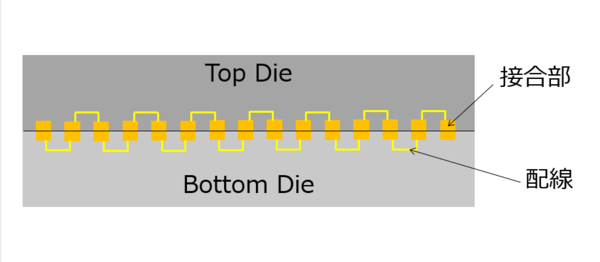

CSAMテストをパスしても、実際にやってみたらTSVの接合不良があった、ということは当然あり得る。特にこれが顕著なのはディジーチェーン、つまり複数のTSVにまたがるように配線がつながるケースである。

この場合、一ヵ所でもTSVの接続が不良だと全体が断線することになる。もちろん実際には接続を一ヵ所だけにするのはリスクが高いので、複数の接続箇所を利用することで、多少の接続不良があっても問題ないように配慮するのが一般的であるが、それはそれとしてテストでは実際にこうしたディジーチェーンの配線をいろいろ用意して歩留まりを確認している。

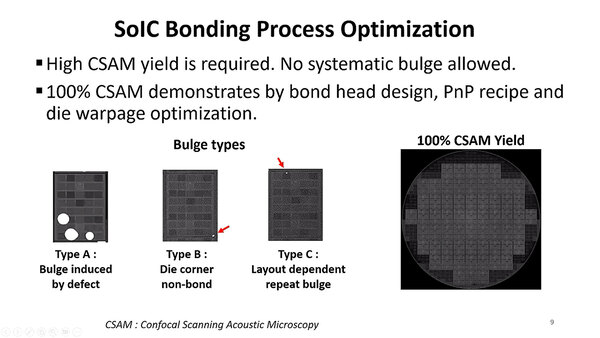

間にごみなどが入っていたりすると、Type A~Cのように見えるので問題があるとわかる。もちろんCSAMですべての欠陥が確認できるわけではないが、逆に言えばCSAMレベルでは100%の歩留まりになるくらいにしないと、量産時の歩留まりが大きく下がることになる

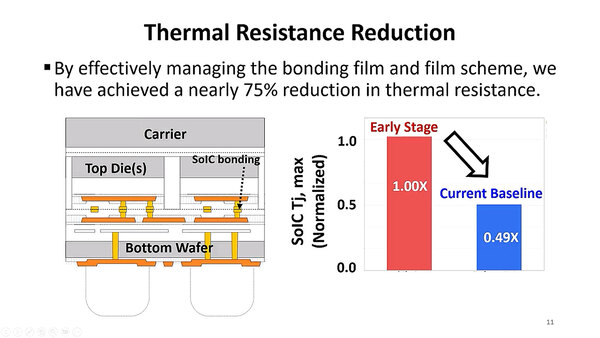

当初は歩留まりが平均70%程度とかなり低い数値だったが、今ではかなり歩留まりを改善できたとしている。またこの際の熱抵抗を、ほぼ半減できたとしている。

右のグラフは、ウェハー全体での歩留まりのもので、初期段階では最悪半分がアウトだったのが、今では悪くても8割は確保できているとのこと。ここまで高ければ、冗長VIAを利用することでほぼ歩留まりを100%に持っていけるだろう

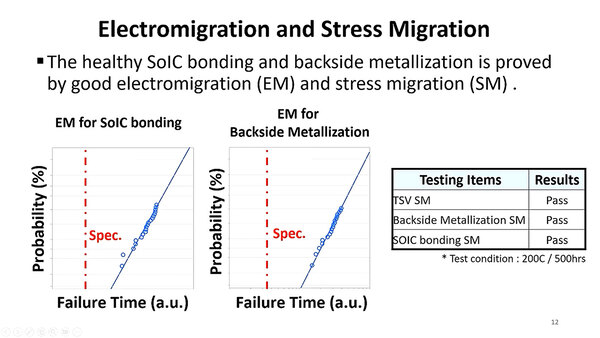

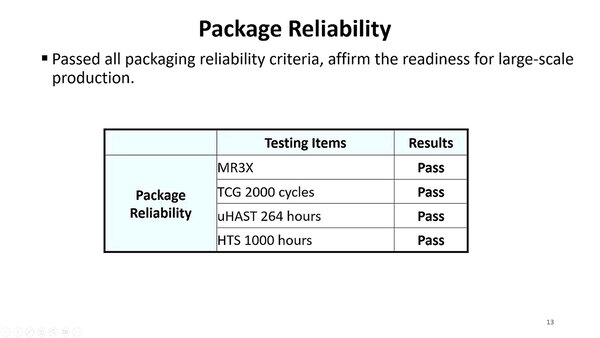

耐久性としては、まずはエレクトロマイグレーション(金属中に電流が流れている時に原子が移動する現象)とストレスマイグレーション(温度を上げたときにストレスが発生し配線が断線する現象)がどちらも基準値を上回る成績を出しているとし、またパッケージの信頼性試験も問題なく通ったとしている。

エレクトロマイグレーションは連載464回などでも説明している。ストレスマイグレーションは機械的振動などによる破壊である。半導体といっても無限に使えるわけではなく次第に劣化していくのは避けられないが、少なくともこの結果を見る限り、先にトランジスタ層の方が劣化して使えなくなりそうだ

MRはMass Reflowで、3回のリフロー(半田槽の中にパッケージを突っ込んではんだ付けする作業)に耐えるというもの。TCGは温度変化、HASTは加速度試験(振動)、HTSは長期間の高温に晒した状態での信頼性をそれぞれ試験する

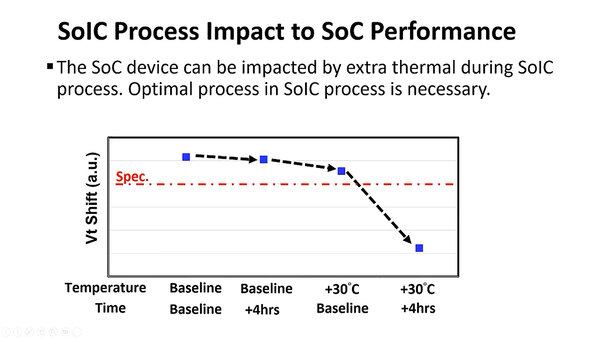

ただ、例えば長時間連続稼働した場合には多少電圧がずれる場合があるとしている。これはチップレット側で対応というよりもSoICプロセスの方の最適化で対応するとしている。

この連載の記事

-

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 -

第855回

PC

配線太さがジュース缶並み!? 800V DC供給で電力損失7~10%削減を可能にする次世代データセンターラック技術 - この連載の一覧へ