ロードマップでわかる!当世プロセッサー事情 第800回

プロセッサーから直接イーサネット信号を出せるBroadcomのCPO Hot Chips 2024で注目を浴びたオモシロCPU

2024年12月02日 12時00分更新

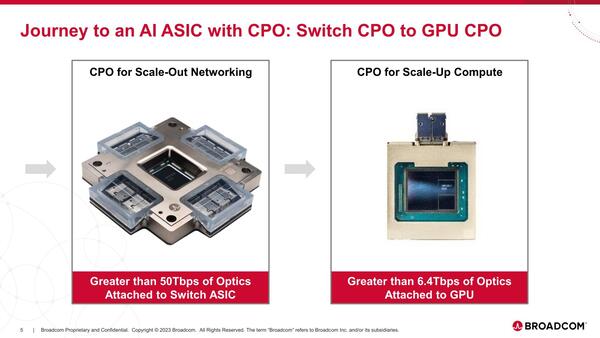

光学部品と電子部品をまとめて一つにした

BroadcomのCPO

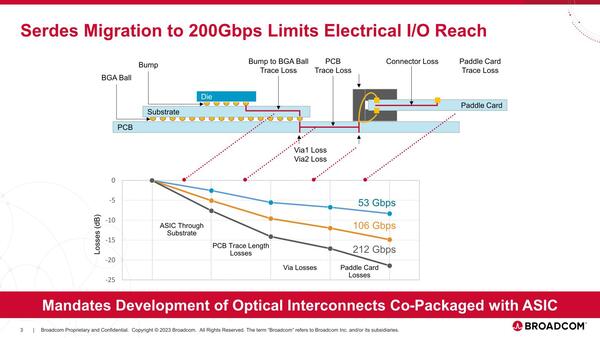

既存の問題は下の画像に示したとおりで、スイッチのチップからトランシーバーモジュールまでの配線距離が長すぎ、しかも信号の高速化にともないどんどん損失が増えることをなんとかしたい、というものだ。

その解決案は、スイッチチップの「すぐそば」でさっさと光化してしまえば、その先の減衰はあまり問題にならないというものである。

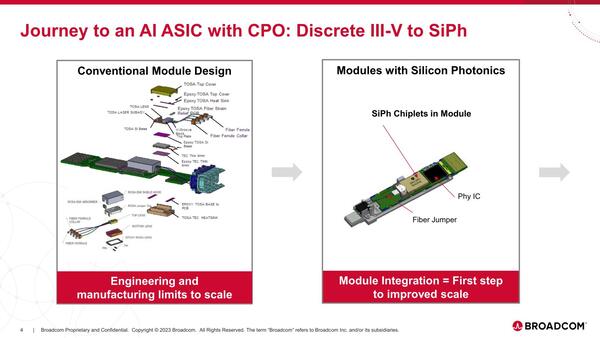

まずはディスクリートの光部品を、SiPh(Silicon Photonics)で置き換える。これはトランシーバーモジュールの光信号変調をCMOSベースの回路で実装するというもので、省電力化・低コスト化が見込める

スイッチチップそのものから光信号を出す、というのは現実問題として問題が多すぎる。いわゆるSilicon Photonicsと呼ばれる、CMOSベースで光信号を扱うための技術そのものは上の画像にもあるようにすでに実用化の域に達している。

ただしCMOSベースといってもそれは最先端の5nmや3nmではなく、それこそ90nmや40nm程度。インテルは研究室レベルの成果として22nmプロセスを利用したCMOSの光アンプを実装したという話を2022年に発表しているが、量産レベルの話ではない。

一方で400Gイーサネットのトランシーバーに入っているDSPは、5nmプロセスなどで製造されて稼働している。これを40nmに持ち込むのは無理である。そこで光学部品と電子部品は別々のCMOSプロセスで製造し、それをまとめて一つの部品にしよう、というのがCPOである。

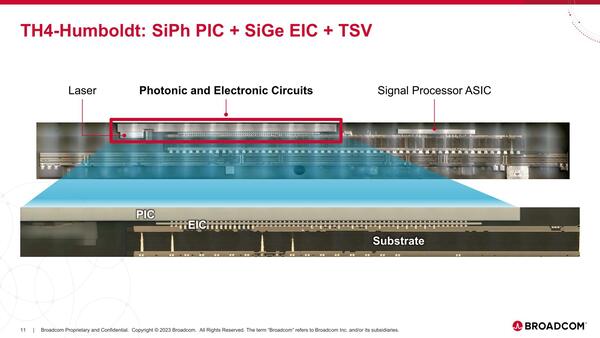

Tomahawk 4(Humboldt)用のCPO断面図。この世代、EICはまだCMOSでは速度が足りなかったためか、SiGeで構成されている。ただしこの次のTomahawk 5ではEICもCMOS化された

上の画像で言うと、スイッチとの接続は右側になる。スイッチから来た信号はまずSignal Processing ASICに入り、ここで変調やコーディング、エラー処理(FEC:Forward Error Collectionと呼ばれる処理)を経てその左のEIC(Electrical IC)に入る。

EICでは先に挙げたGearboxなどの処理を行ない、例えば50Gbpsの信号×8を400Gbpsの信号に変換したうえで、TSV経由でEICの上のPIC(Photonics IC)に信号を伝える。PICでは電気信号を光信号に変調する。

具体的に言えば、CPO左下にある"Laser"(光の生成源)からの光を受けて、電気信号にあわせてその光をOn/Off(厳密にはこれもPAM-4なので、4レベルの強度に変換)する形で光信号化し、それを外部に出力するかたちだ。

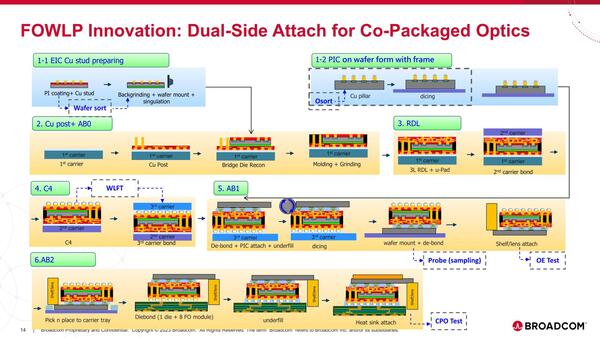

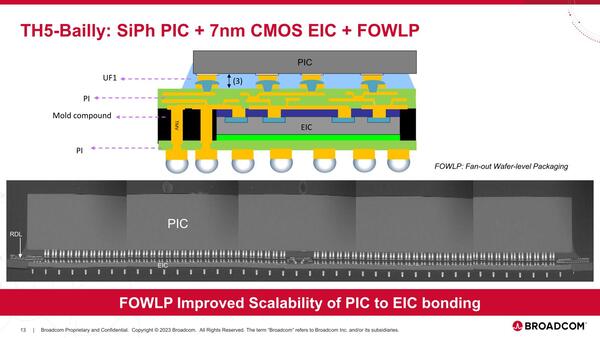

現時点で最新のTomahawk 5ではこのCPOのうちEICが7nm CMOSに変わっており、またパッケージにFOWLP(Fan-Out Wafer Level Package)を採用している。

FOWLPは台湾ASEが2016年に実用化しているが、現状FOWLPはASE以外にも多くのOSATがサービスを提供しており、TSMCのInFOもFOWLPとみなせるので、製造がどこかはこれだけでは不明である。構造を変えたのは、おそらく低コスト化(TSVはどうしても高価になる)であろう

CPOの製造方法を示したのが下の画像だ。EICをまず作り、これにPICをひっくり返して重ねるかたちだが、途中にキャリア(製造途中に使われる土台)を3つも必要とするあたり、なかなか大変である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ