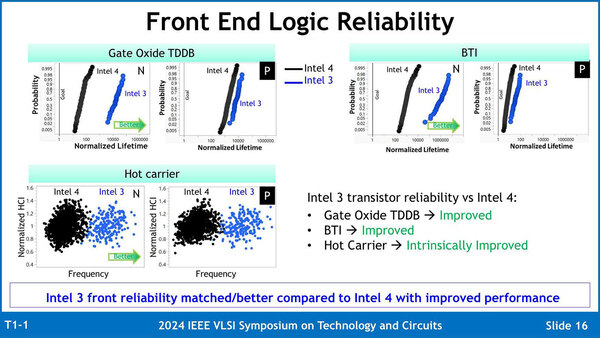

トランジスタまで含めた信頼性が大きく改善

次が信頼性周りの話。1.2V Cellの信頼性の話は連載777回で説明したので割愛するとして、通常のトランジスタまで含めての信頼性の話が下の画像だ。

| 起こり得る現象 | ||||||

|---|---|---|---|---|---|---|

| Gate Oxide TDDB(Time Dependent Dielectric Breakdown) | ゲート酸化膜経時破壊。ゲート酸化膜の耐圧電圧以下であっても、ずっと電圧を掛け続けるといつかは破壊される現象 | |||||

| BTI(Bias Temperature Instability) | バイアス温度不安定性。チップの温度が上昇すると、特にPMOSでは閾値電圧の絶対値が段々大きくなり、特性が変動するという現象 | |||||

| HCI(Hot Carrier Injection) | ホットキャリア注入。運動エネルギーを得た電子あるいは正孔がゲート酸化膜をトンネルしてリーク電流などになる現象 | |||||

まず最初の2つについてはこうした現象が発生するまでの時間がだいぶ改善している。またHCIに関しては、同じHCIの発生率に対してより動作周波数を上げられるようになったことが観測されている。FETもある意味、機械部品であり、ずっと使っていれば次第に劣化していくことは避けられないのだが、その劣化の度合いがだいぶ改善した、という話である。

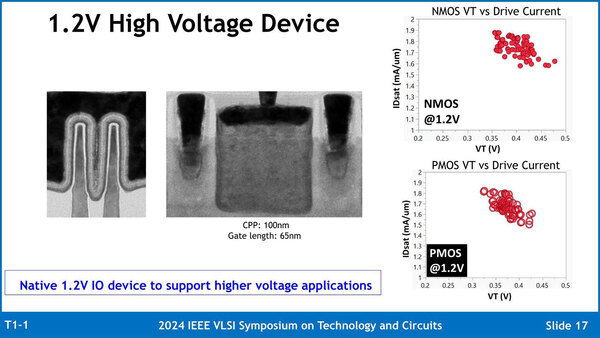

説明では次に1.2V Cellの話に移るのだが、これも連載777回で紹介したので割愛する。ただその1.2V Cellの断面写真が示されていたので紹介しておきたい。

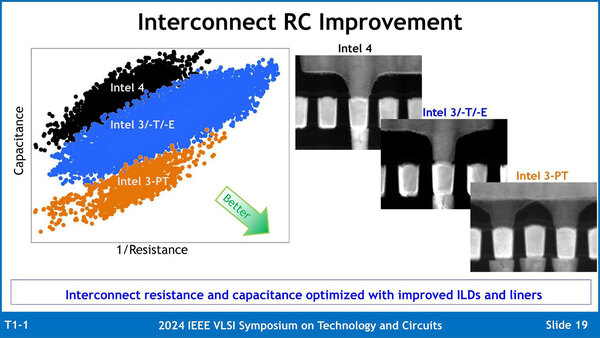

最後にIntel 3-PTの話である。先にIntel 3-Eの高性能版と説明したが、具体的な話としてインターコネクトの改良が紹介された。ただIntel 3-Eと3-PTの違いが単にインターコネクトだけなのか、ほかにトランジスタの改善なども含まれるのかは不明だ。

Intel 3-PTのインターコネクト。この写真だけ見ると、配線層の高さが詰まる方向になり、かつ配線密度も上がっているように見受けられるのだが、具体的な話がなく単にRC特性の改善としか説明されていない

ということで、VLSI Symposiumにおけるインテルの発表を簡単にまとめてみた。問題は歩留まりや現在のウェハー生産能力なのだが、このあたりの情報は当然ながら公開されていない。Intel 3の出来具合がXeon 6の性能や供給体制に大きく関わってくるだけに、順調に生産できていることを祈るのみである。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ