ロードマップでわかる!当世プロセッサー事情 第721回

性能ではなく効率を上げる方向に舵を切ったTensilica AI Platform AIプロセッサーの昨今

2023年05月29日 12時00分更新

連載717回でSynopsysを取り上げたので、片割れであるCadenceを取り上げないのは片手落ちだろう。ということで今回はCadenceが提供するTensilica AI Platformを紹介したい。

命令セットを自由に組み替えられる

自由度の高いプロセッサー「Xtensa」

Tensilicaは1997年にサンノゼで創業された。創業者はChris Rowen博士であるが、Rowen博士はMIPS Computer Systemsの創業者の1人でもあり、SGIによる同社の買収後はしばらくSGIに在籍するものの、その後Synopsysに転職。そして1年で辞めて立ち上げたのがTensilicaである。

そもそもRowen博士はMIPS Computerを立ち上げたくらいなので32bit汎用RISCプロセッサーの特徴や長所短所はよく理解している。そしてSynopsysでIPというビジネスを学んだことで、独特のアーキテクチャーを持つプロセッサーをIP売りする、というビジネスを思いつき、これを実現するために立ち上げたのがTensilicaというわけだ。

そのTensilicaの最初のプロセッサーであるXtensaの特徴はASIP(Application-Specific Instruction set Processors)である。要するにアプリケーションの要件に合わせて命令セットを自由に組み替えられるというものだ。

Xtensaは「強いて言えば」VLIW+Vectorの構造になる(厳密にはRISC的な要素もあるのだが、無理に分類すればVLIW+Vectorにならざるをえない)が、その命令セットどころか命令長まで自由であり、同じXtensaでも、それこそASICごとに命令セットにはまったく互換性がない。

ちなみにXtensaはCPUだけでなくDSP(Digital Signal Processor)も利用可能で、どちらか(あるいは両方)を使うか否かも自由に選択できる。それもあってデザイン手法も独特だ。

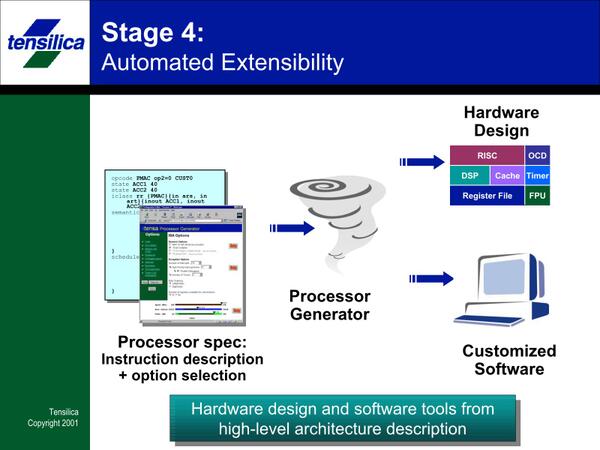

一番無難な方法は、Xtensa Processor Generatorと呼ばれているツールを使って命令セットや構成を設計し、ここからプロセッサーのIPを生成するとともに、そのプロセッサーIPをサポートするソフトウェアを自動作成するというものだ。

なぜいきなりStage 4か? というと、Stage 1はありもののCPUを使う、Stage 2はARMなどのIPのライセンスを受けてそのまま使う、Stage 3はセミカスタムのIPを使うというものがあり、その次に来るものだからという話である。ちなみにStage 3で例に挙げられていたのがARC InternationalのARCtangentであるあたり、お互いを強く意識し合っていたのがわかる。

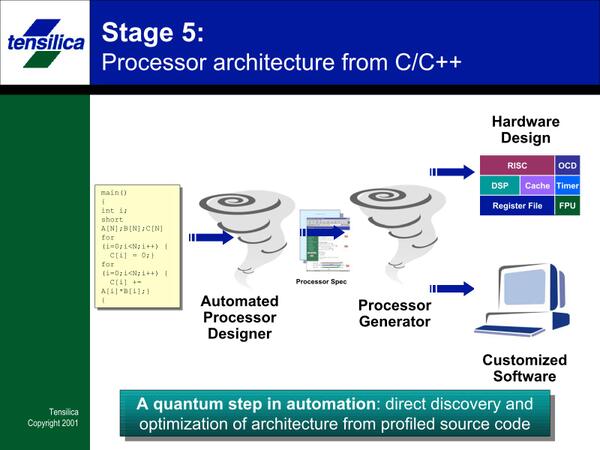

Tensilicaはさらにそこから一歩進んで、アプリケーションプログラムからそれに合わせたアーキテクチャーを生成するというオプションまで提供していた。

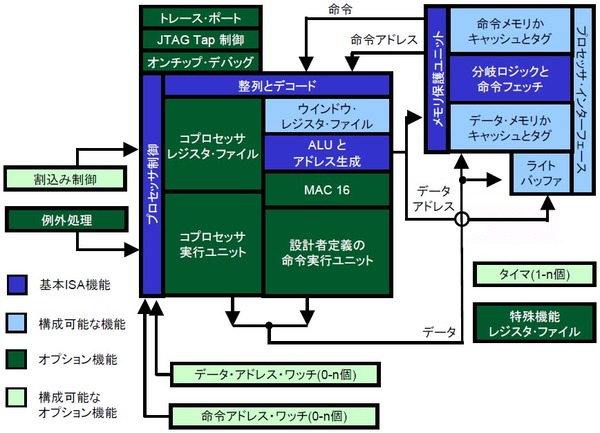

下の画像は2000年頃にあったTensilicaの日本語カタログ(当時は横浜に日本オフィスも構えていた)からの抜粋だが、かなり好きなように内部構成を変更できる仕組みなのがわかる。

ちなみに上の画像の構成をサポートして実際に稼働させられるXT-1000というボードも当時発売されていた。これは主に評価用で、まだ当時のことなのでXilinx/Alteraともに大容量のFPGAはラインナップしておらず、それもあってXT-1000はAlteraのCPLDを2つ搭載し、ここにXtensaを載せて稼働させる形だった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ