ロードマップでわかる!当世プロセッサー事情 第707回

Xeon W-3400/W-2400シリーズはワークステーション市場を奪い返せるか? インテル CPUロードマップ

2023年02月20日 12時00分更新

連載702回でも言及したが、Sapphire Rapidsを利用したXeon W-3400/W-2400シリーズが2月15日に発表になった。発表こそ2月15日だが出荷は3月に入ってからとなっており、入手にはもう少し待つ必要がある。今回はその発表内容を解説しよう。

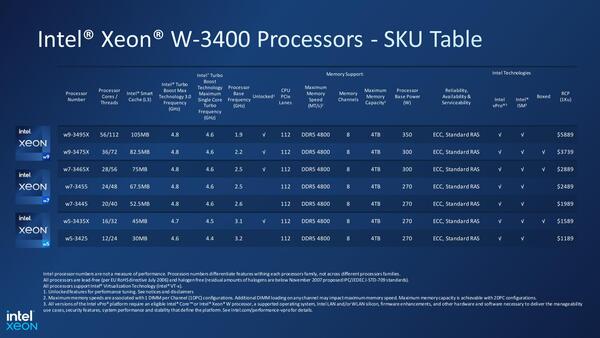

Xeon W-3400/W-2400シリーズは合計15SKU

まずSKU一覧から。Xeon W-3400シリーズはw9が2製品、w7が3製品、w5が2製品の合計7製品、Xeon W-2400シリーズはw7が2製品、w5が3製品、w3が3製品の合計8製品で、シリーズ全体では15製品となる。実は情報サイトなどでは、Xeon W-3400シリーズにはこの他に以下の2製品があり、トータル17製品という話が流れていたのだが、こちらは正式なラインナップには入っていない。

Xeon w5-3433 16core/32thread 2.0/4.2GHz TDP 270W

Xeon w3-3423 12core/24thread 2.1/4.2GHz TDP 220W

Xeon w3-2423があるあたりは“23”というモデルナンバー自体はあり得る話で、おそらくラインナップの検討の中で最終的に消えたものと思われる。

さて、端的にW-3400シリーズとW-2400シリーズの違いを言えば、コアがMCCかXCCかということになる。Intel Arkによれば、Xeon W-2400シリーズはPackage CarrierがE1B、W-3400シリーズはE1Aとなっており、一方第4世代Xeonの場合MCCのものはやはりE1B、XCCのものはE1Aと記されているので間違いないだろう。余談だがXeon MAXの場合、Package CarrierはE1Cとなっている。

したがってベースは第4世代Xeon Scalable、つまりSapphire Rapidsベースなわけだが、Xeon Scalableとの違いは以下のとおりで、ワークステーション向けに必要な機能のみを残したという感じだ。

- 全製品1ソケットのみ。2ソケット以上での接続用のUPIリンクは全SKUで無効化されている。

- Optane Persistent Memory 300シリーズのサポートはなし。

- 搭載されているアクセラレーターに関しては、DSA(Data Streaming Accelerator)が1基のみ有効化されており(Xeon Scalableは4基搭載されている)、その他のアクセラレーター(QAT/DLB/IAA)は無効化されている。

- セキュリティー/管理機能も大幅に簡素化。VPro EnterpriseおよびAMT(Active Management Technology)は搭載されている(逆にこの2つはXeon Scalableにはない)し、Platform Firmware Resilience SupportやCFE(Control-Flow Enforcement Technology)、TME(Total Memory Encryption)などは有効になっている一方、Crypto Acceleration/SGX(Software Guard Extensions)/TDT(Threat Detection Technology)/RPE(Remote Platform Erase)/One-Click Recoveryなどの機能は無効化されている。

- Xeon Scalableは全製品倍率ロックがかかっているが、Xeon Wの方は一部SKUに倍率アンロック版が提供される。

では次にW-2400シリーズとW-3400シリーズの違いをみると以下のとおりになっている。

- 「相対的に」W-3400シリーズの方が多コア。W-2400シリーズは最大24コアまでとなっている。

- W-2400シリーズはメモリーが4chに制限されており、また一部のSKUはDDR5-4400までの対応である。一方W-3400シリーズは8chで、全製品DDR5-4800までの対応となっている。

- メモリーch数に絡む話だが、W-2400は最大メモリー容量が2TBに制限されている。一方W-3400シリーズは4TBまでサポートされる。

- CPUから出るPCIeレーン数は、W-2400が64レーン、W-3400は112レーンになっている。

パッケージそのものは(内部に相違はあるとは言え)同じLGA4677なので、マザーボードは基本的には共通(Xeon W-3400に寄せてある)で、ただしW-2400シリーズでは利用できないDIMMスロットやPCIeスロットが出る、という形になると思われる。

これは別に珍しくない。もう古い話になるが、第1世代のCore-Xの場合、Core i7-7xxxシリーズはDDR4が2chでPCIeは16/28レーン、一方i9-7xxxシリーズはDDR4が4chでPCIeは44レーンだったが、どちらもソケットはLGA2011で共通だった。これと同じ仕組みが今回も採用された格好という程度で、後はコア数と動作周波数が違うのみだ。

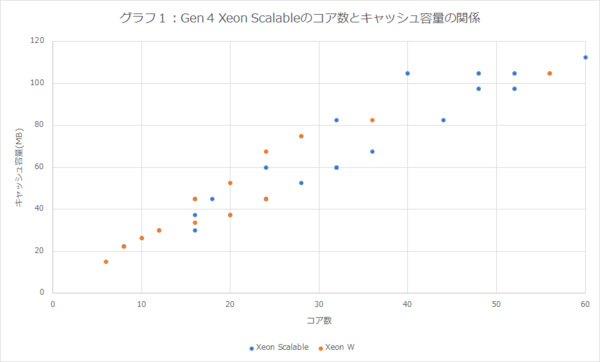

3次キャッシュの容量は「原則として」コアの数に比例した量になるのだが、これがわりと恣意的というか、少しおもしろい傾向にある。計算してもらうとわかるのだが、W-2400シリーズもW-3400シリーズもトップエンドは1.875MB/コアなのだが、下位モデルほど容量が増える傾向にある。実はこれ第4世代Xeon Scalableも同じである。

下のグラフは第4世代Xeon Scalable 47製品(Xeon MAXは除く)とXeon W 15製品について、グレード(Platinum/Gold/Silver/Bronze/W-2400/W-3400)は無視してコア数と3次キャッシュ容量を書き出したものである。

基本は1.875MB/コアという容量(グラフ中の破線)ながら、中にはこれを超える製品がいくつかあるのがわかる。実際16コアの場合では3次キャッシュ容量が以下の4種類あったりする。

| 16コアモデルの3次キャッシュ容量 | ||||||

|---|---|---|---|---|---|---|

| 3次キャッシュ容量 | モデルナンバー | |||||

| 30MB(1.875MB/コア) | Xeon Gold 5416S/Xeon w5-3435X | |||||

| 33.75MB(≒2.109MB/コア) | Xeon w5-2465X | |||||

| 37.5MB(≒2.343MB/コア) | Xeon Gold 6426Y | |||||

| 45MB(2.8125MB/コア) | Xeon Gold 6444Y/Xeon Gold 8444H | |||||

要するにコアは無効化しても3次キャッシュは有効化したままにすることで、3次キャッシュ容量を稼いでいるわけだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ