自動運転をターゲットとしたAIプロセッサーを開発

VSORAは2018年あたりまではそれこそ通信分野などに向けた信号処理をメインとしていたわけだが、2019年あたりから“A New DSP Approach to Accelerate 5G and AI Design Development”と、ターゲットとする市場に“AI”の文字が入るようになり、2020年になると“AI & Signal Processing/ADAS/Digital Communication”とターゲットにADASが入るようになり、2021年にはついにDigital Communicationの文字が消え、代わりに自動運転をターゲットとしたAIプロセッサーであるTyrを前面に押し出すようになった。

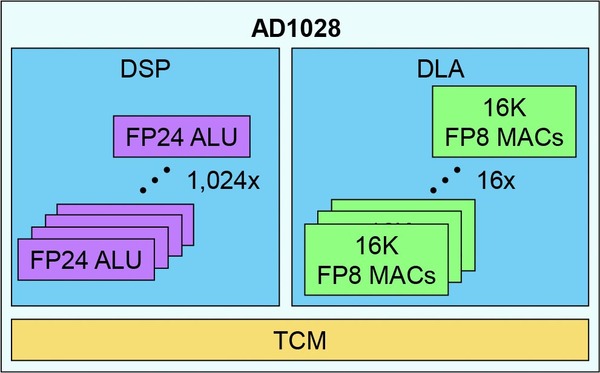

その2020年、AI向けとしてVSORAが発表したのがAD1028である。AD1028は、FP24(16bit仮数+7bit指数+符号)のALUを1024個並べたDSP部と、FP8のMAC演算を16K個同時に演算可能なMACアレイを16個(つまり1サイクルあたり256K個の演算が可能)搭載したDLA部、それにTCM(Tightly Coupled Memory)を組み合わせた構成である。

ちなみにAD1028はVSORAではミッドレンジ向けという扱いであり、ハイエンドは2048 ALUのDSPと512K MACを搭載したDLAから構成されるAD2056という製品が予定されていた。

もっともこのAD1028、2020年の時点で7nmプロセス向けにテープアウトしており、2GHz動作で1PFlopsの演算性能(DLA部:DSP部は4TFlops)を持ち、消費電力は35W未満。ダイサイズはTCMを除いて35mm2とされていた。実際にはこれだけの演算性能を持たせるとなると、相当なサイズのメモリーが必要になる。VSORAの推奨によれば、AD1028の構成であればおよそ105MBのTCMが必要、という計算だそうである。

ちなみにラフな計算であるが、同じく7nmで製造されるRyzen 5000シリーズに利用されていたZen 3コアのL3(32MB)のエリアサイズがおおむね36mm2なので、同じ形で実装すると105MBではおよそ118mm2ほど。それとAD1028自身の35mm2とあわせてダイサイズは153mm2とけっこう大きくなる。

ただSRAMなので消費電力はそれほど大きくはならない。VSORAはこのAD1028で30TOPS/Wを実現できるとしているが、厳密に計算すれば29TOPS/W弱といったあたり。30TOPS/Wも誇大表現とは言い切れない程度、といったところか。たぶんSRAMも込みにして40W程度、実質25TOPS/Wあたりが現実的な線だろう。

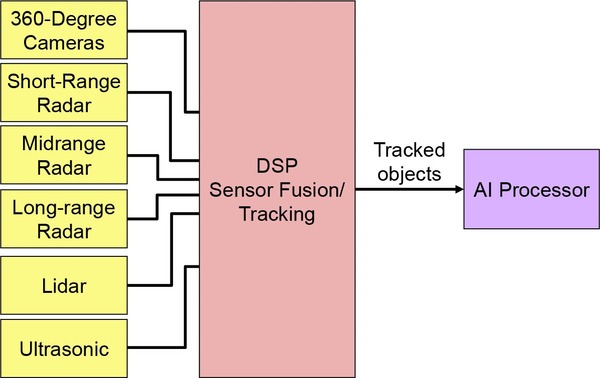

なぜDSPとTLAの2ブロックが必要か? という理由が下の画像だ。VSORAはLevel 4の自動運転をターゲットに置いており、ということはさまざまなセンサー(カメラや長/中/短距離レーダー、LiDAR、超音波センサーなど)を使ってまず周囲や進行方向の状況を取得、これをベースに自動運転の判断を行なう必要がある。そこでまずDSP部で、こうしたさまざまなセンサー情報を処理し、この結果をDLA部を利用して処理する、という構成を狙ったわけだ。

ちなみにVSORAによればDSP部は複雑な処理も可能な汎用のALUをベースにした構成だそうだが、DLA部はもう完全にMAC演算に特化した構成のようで(アクティベーション用の関数があるかどうかも不明)、MACを制御するコントローラーにあたるものがなにかしら搭載されていないとやや処理的に厳しい(これを全部外部のホストから行なっていたら、そこがボトルネックになる)気がするのだが、そのあたりの詳細は一切公開されていない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ