ロードマップでわかる!当世プロセッサー事情 第677回

アナログ回路でデジタルより優れた結果を出せるAspinityのAnalogML AIプロセッサーの昨今

2022年07月25日 12時00分更新

今回取り上げるのはAspinityのAnalogMLである。“AnalogML”という言葉からもわかるように、アナログコンピューターを実装している。アナログコンピューターといえば連載591回で紹介したMythicはフラッシュメモリーをベースとしたアナログコンピューターとしていいだろうが、Aspinityの実装はまた異なったものである。

Aspinityのターゲットは

センサー向けなどの常時利用を想定したAI市場

Aspinityは2015年創業の会社である。会社は少し珍しくペンシルバニア州ピッツバーグである。Google マップで見てみると、レンガ造りのやや時代を感じさせる2階建ての雑居ビルで、1階には小売店が入ってるという、ハイテク企業とは思えない立地なのが一周まわってむしろ格好良いかもしれない。

ちなみに個人的にペンシルバニアと言うと、NYC(ニューヨークセントラル鉄道)と壮絶な争いを繰り広げたPRR(ペンシルバニア鉄道)しか思いつかないあたりは、ちょっと自分でも偏っている自覚はある。

話を戻そう。Aspinityの創業メンバーはTom Doyle氏(CEO)、Brandon Rumberg博士(CTO)、David Graham博士(CSO)の3人である。Doyle氏はParagon IC SolutionsというEDAツールの会社を起業後、Cadenceで12年程を過ごしてからAspinityを立ち上げており、Rumberg博士とGraham博士は共にウェストバージニア大学からの参加である。ちなみにGraham博士はウェストバージニア大の教授も兼業されている。本社がピッツバーグにあるのは、このあたりも関係しているのかもしれない。

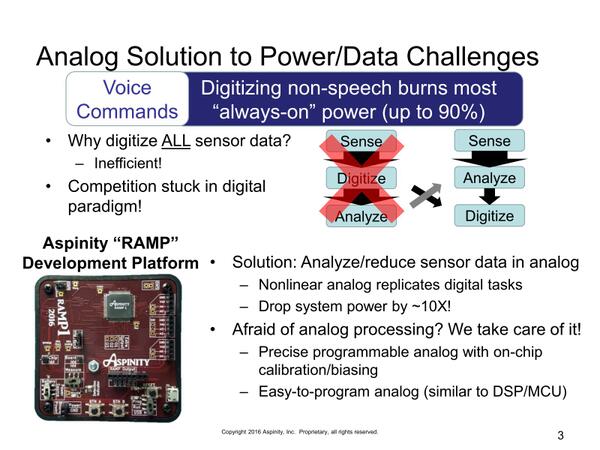

さて、Aspinityがターゲットとしているのは、センサー向けなどの常時利用を想定した、エンドポイントAIの市場である。例えば振動センサーだったり画面やボタンのタッチ、あるいは音声などを検出して動かしたりという用途はかなり広範に存在しているが、これを従来型の技術(下の画像左側)でやった場合、以下の問題がある。

- 常時マイコンかなにかを動かす必要があり、これの待機時消費電力が馬鹿にならない。

- センサー出力は基本アナログなので、ADC(アナログデジタル変換)に消費電力を常時喰われる。

センサーそのものの消費電力は(モノによって差があるが)おおむね100μW程度だが、ADCには(これもモノや精度・頻度で差があるが)最大600μW、MCUは3mWほどを消費することになる。もちろん外部電源が利用できる環境ならこの消費電力は無視できるレベルだが、バッテリー駆動だとそうもいかない。

連載665回でIntel GNAを紹介したが、あれも根っこは同じで常時Windows Helloを動かしていたらいかにノートPCといえどもバッテリーの減りが深刻なものになる。必要があるまで本体のCPUを動かさずに保つために、カメラとCPUの間にGNAを入れることで待機時の消費電力カットを目論むものだが、Aspinityのアイディアも同じである。

Aspinityの場合、ADCと「データの判断(マイコンを起動してデータ処理させるべきか否かを決定する)」の2つの役割を、40μW未満という非常に少ない消費電力で実現することを狙ったチップとなっている。

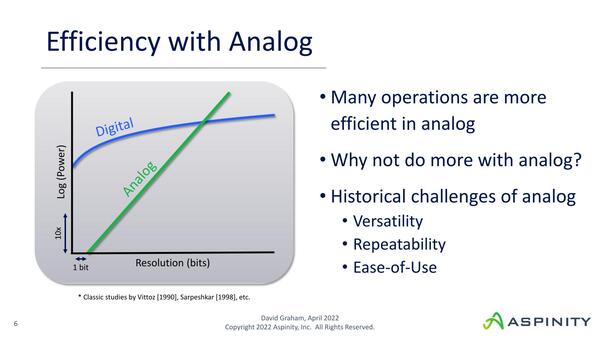

ではAspinityはなぜアナログコンピューターを目指したか? という理由が下の画像だ。要するにある程度以上データ量が増えてくると、処理方式としてはデジタルの方が有利になる。逆に言えば、データ量が少ない場合は圧倒的にアナログ処理の方が有利になる。それにもかかわらず、大局的な流れで言えばアナログからデジタルへの移行が明確である。

理由はやはり上の画像にあるように汎用性や再現性の高さ、あるいは実装の容易性によるところが大きい。アナログがデジタルに置き換えられつつあるのは、十分な時間をかけて作り込めばアナログの方が高効率な回路を実現できるが、アナログで簡単にパパっと組んだ程度ではいろいろ問題が出ることが多く、それで問題ないというケースは普通ない。

ところがデジタルではそういったケースでもそこそこカバーできてしまうわけで、端的に言えば技術力のないエンジニアでもそこそこ使えるものが用意できるというのは、昨今のアナログに詳しいエンジニアが不足気味の業界にとっては福音以外の何物でもない。

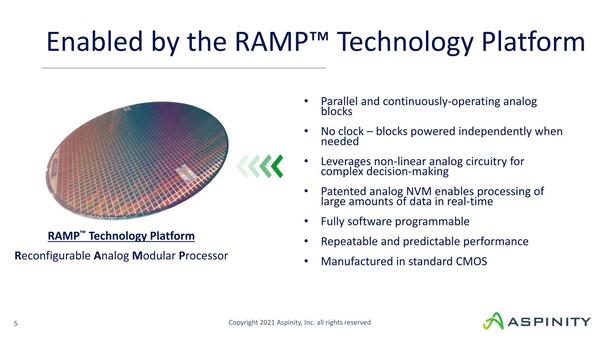

ただ逆に言えば、このあたりをなんとかすればアナログベースでデジタルの同等回路よりずっと優れた結果を出せることになる。これに向けてAspinityが開発したのがRAMP(Reconfigurable Analog Modular Processor)である。

このRAMPの詳細はいまだもって説明されていないのだが、説明を読む限りにおいてはFloating GateベースのNANDフラッシュメモリーを利用してアナログ回路と同等のことが可能で、これを組み合わせるとさらに複雑なことができるとしている。

「アナログ回路と同等」といっても、たとえばNANDフラッシュのセルで抵抗やコンデンサーのシミュレーションをするなどという話ではなく、NANDフラッシュのセルを組み合わせてフィルター回路や包絡線検波(Envelope Detector)など、既存のアナログ回路と同等の動きをさせるものと考えた方が良いようだ

連載591回のMythicは、NANDフラッシュのセルを可変抵抗として扱う仕組みでCR回路を構築していたが、RAMPはもう少しFPGAのセル的な意味合いが強いように思える。RAMPそのものは、2016年に最初の試作チップが完成しており、これを利用して同社のアイディアの実現可能性はすでに確認されていたそうだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ