サーバー向けの機能を実装

先ほど後回しにしたS1/S2だが、以下のようになっている(どちらもオプション扱い)。

| S1/S2の仕組み | ||||||

|---|---|---|---|---|---|---|

| S1 | CARD_PWR_STABLE | |||||

| S2 | CARD_CBL_PRES# | |||||

まずCARD_PWR_STABLEだが、これはSense0/1とは逆に、AICから電源に対して「電源供給状態が良好である」ことを通知する。具体的には、電源が供給する電力枠内でAICが正常に稼働していることを通知する仕組みである。ついでCARD_CBL_PRES#だが、こちらもやはりAICから電源に対して通知する配線である。このCARD_CBL_PRES#には以下の2つの目的がある。

- 12VHPWRコネクターが正しく接続された事をAICから電源に通知する

- AICから電源あるいはホスト側のコントローラーに対して、AICが存在することと、Power Budgeting Sense Detect Registerを搭載していることを通知できる。これを利用することで、システムはどのスロットにどんなAICが装着され、どの電源ケーブルが装着されているかを認識できる

先ほど最大出力をダイナミックに変更できる機能があるという話があったが、この規定は複数スロットに消費電力が大きなAICが搭載されているという、デスクトップというよりはサーバー向けの要望に沿ったものだ。

この場合、システムが立ち上がったら電源(とシステム側のコントローラー)は、どのスロットにどんなAICが装着されているかを自動的に認識し、最適な電源出力を行なえるように調整したうえでシステムをスタンバイ→復帰させると、最適な出力になるというわけだ。一般のPCでは使われることはなさそうな機能である。

なおS3/S4の、つまりSense0/1を認識しないAICの場合、利用できるのは最小の150Wに抑えられるという規定もある。これは既存の2×4pinコネクターを2×6pinコネクターに変換するようなアダプターが出てくることを想定してのものと思われる。

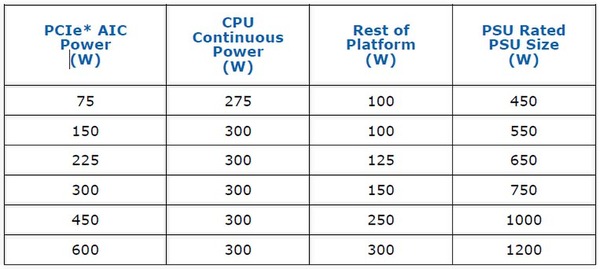

ちなみに600W出力が可能な電源の要件はないのだが、普通に考えるとこんな構成になる、という例が下の画像だ。

PCIe AIC Powerは2×3/2×4/2×6のいずれか(もしくは複数の組み合わせ)でPCIeカードに供給される電力、CPU Continuous PowerはCPU(とおそらくメモリーサブシステムなどを含む、要するにマザーボード)に供給する電力、Rest of PlatformはSSDやファン、その他の周辺機器への電力の合計、PSU Rated PSU Sizeというのは俗に言われる電源容量である。12VHPWRで600Wを供給する電源は、1200W以上になるだろう、というのが1つの目安となっているわけだ。

ここまでの話はATX 3.0 Rev 2.0をベースに説明してきたが、ATX12VO 2.0についてもまったく同じである。つまり、既存のATX12VOに、この12VHPWRの規定を追加したのがATX12VO 2.0である。

今のところATX12VO 2.0に対応したビデオカードを含むPCIeの拡張カードは存在しないが、インテルはAlder LakeですでにPCIe 5.0対応を果たしているし、AMDもZen 4世代でPCIe 5.0への対応を明らかにしているので、AMD/NVIDIAともに次世代のハイエンド製品はPCIe 5.0への対応と併せて12VHPWRコネクターを採用してくるかもしれない。

むしろ問題はATX12VOの普及の遅さであるが、今回インテルはMSIのCreator P100AとMPG Trident ASがATX12VOを採用したことを明らかにしている(ATX12VO 2.0ではない)。

ただ逆にいうとこれだけという話であって、かつてのBTXみたいな雰囲気になっているのだが、果たしてこれに続くベンダーはどの程度出てくるのだろうか?

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ