新年早々の1月6日、DEC→AMD→SiByte→P.A.Semi→Apple→AMD→Intelと放浪の旅(?)を繰り返していたJim Keller氏がPresident兼CTOとしてTenstorrentに入社したことが報じられた。

CTOになったとはいえ、そもそもの入社は2020年12月で、まだ入社して1ヵ月になるかならないかという期間なので、今の時点でTenstorrentのテクノロジーになにかしらの影響を与えているかと言えばほぼ0だとは思うが、それはともかくとしてKeller氏を引き寄せるようなおもしろいモノがTenstorrentにはあった、ということの傍証ではあるかと思う。

推論と学習、両方のAIプロセッサーを開発する

Tenstorrent

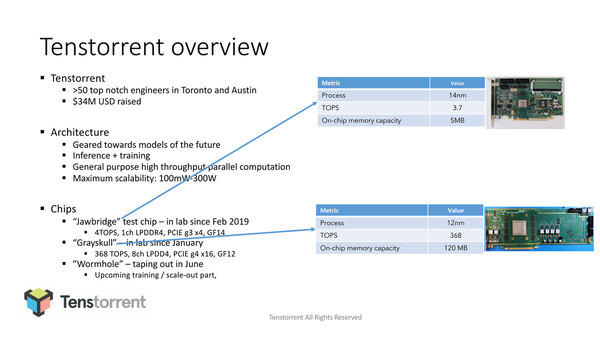

Tenstorrentは2016年3月にカナダのトロントで創業したメーカーである。創業者はLjubisa Bajic氏(CEO)、Milos Trajkovic氏(Director Hardware Engineering)とIvan Hamer氏の3人である。実はこの3人、いずれもAMD(Bajic氏はDirector, IC Design/Architect、Trajkovic氏はFirmware Design Engineering Manager、Hamer氏はConsulting Software/Embedded Engineer)を同時期に辞職して創業した形である。

創業はそんなわけでトロントであるが、現在はテキサス州オースチンにもオフィスを持っており、両方合わせておおむね70人(2020年8月現在:2020年4月には50名超だった)の人員を抱えている。

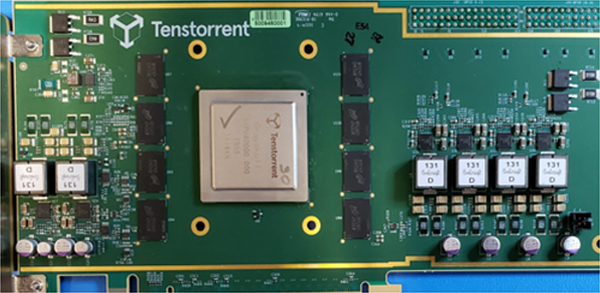

そのTenstorrentであるが、Inference(推論)とTraining(学習)の両方を視野に置いている。そしてすでにJawbridgeとGrayskullという2種類のチップを製造しており(これはどちらもInference向け)、続くTraining向けのWormholeもすでにテープアウトが完了したことを発表している。

コード名の由来は1982年にMattel社が発売した“Masters of the Universe”シリーズのコミック&アクションフィギュアから始まるシリーズのようだ。舞台となる惑星EterniaにはCastle Grayskullなる要塞があり、その要塞の入口の名前がJawbridgeである。で、主人公のHe-ManとShe-Raの母親は元宇宙飛行士で、Wormholeを通ってEterniaに落ちてきたという設定になっている

チップの話はあとでするとして、“Geared towards models of the future”という言葉に、なんというか意気込みというか黒雲というか、なんとも言えないものを感じる。

まずはそのなんとも言えない方の話を先に紹介しよう。2020年8月のHotChips 32において、Tenstorrentは“Compute substrate for Software 2.0”と題した講演を行なった(*1)。Software 2.0と聞くと連載595回のDataflowを思い出すのだが、TenstorrentはDynamic ExecutionこそがSoftware 2.0であると力説する。

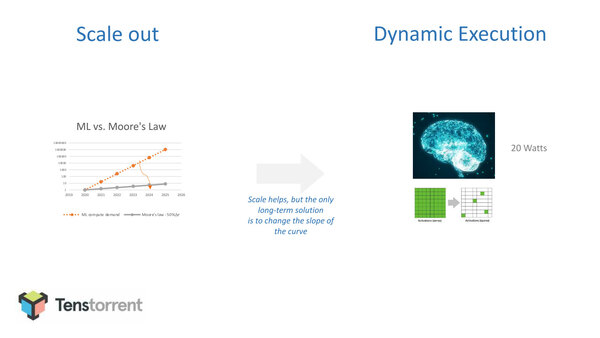

ムーアの法則と機械学習の要求するプロセッサー性能の乖離が激しいことへの解の1つはスケールアウトだが、長期的には役に立っても短期的な解決にならず、これをDynamic Executionが救うという趣旨。ちなみに20Wというのは人間の脳の消費エネルギー(の電力換算)である

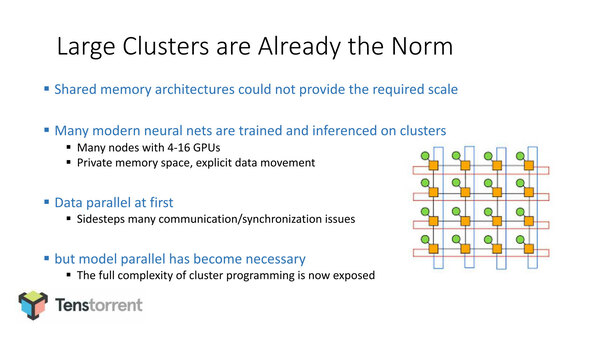

まずスケールアウトについては、すでに広範に使われているが、最初こそデータの並列性だけでいけるものの、すぐにモデルの並列性も必要になるとする。

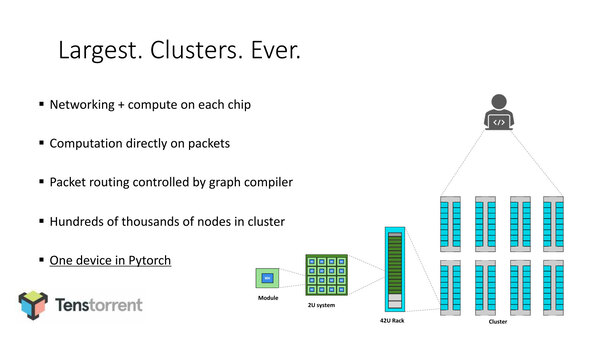

そもそも現在のスケールアウトの使われ方だと、Computation(計算)をするチップは山ほどあるのに、それをコントロールしてるのはPytouchを動かしてる1台のノートなんてこともしばしばあるわけで、はたしてこうした使い方だけが未来か? と言われると確かにもう少し考えたくなる。

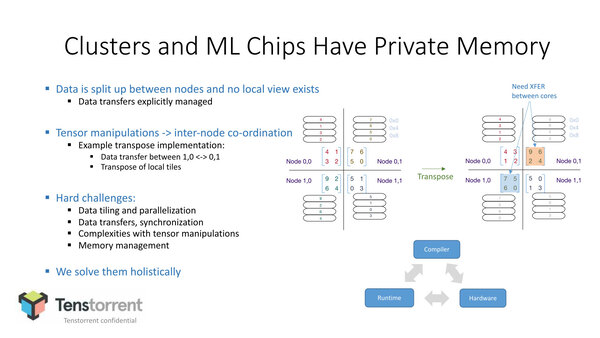

またメモリーアクセスを考えた時、行列に対して行単位のアクセスは連続しているからシーケンシャルアクセスが効くが、行列を転置するとランダムアクセスになってしまう。悪いことに、同じ行列を転置してまた戻して、という操作が入ると同じメモリー領域にシーケンシャルアクセスとランダムアクセスが集中することになりかねず、これが大きく性能を落とす要因になる。

これをうまくさばくためには、メモリーアクセスのループを上手くハンドリングする必要がある。ならばPrivate Memoryを持たしてSharedをやめれば、というとこちらはこちらでノード間にまたがる場合にいろいろ問題が出てくることになる。これを解決するのがDynamic Executionである、というのが同社の説明である。

Private Memoryのマシンで、各ノード間にまたがるデータなどがなければこれでいいのだろうが、あいにくInferenceにしてもTrainingにしても、実際にはノード間でまたがるケースが非常に多い。これをどう解決するかはいろいろな方法が考案・実装されているが、今のところ決定打はない

(*1) なぜか分類がDay 2の"FPGAs and Reconfigurable Architectures"になっているのが謎。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ