小型、高性能化した

HP 9000シリーズを出荷

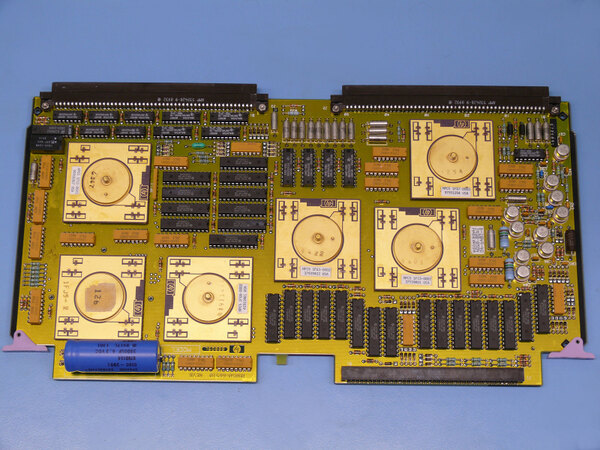

CS-1に続き、当時としてはもう少し現実的なNMOS(NMOS-III:1μmプロセス)を利用して製造されたのが1987年のNS-1である。

画像の出典は、Wikimedia Commons

こちらは最大で30MHz駆動が可能とだいぶ高速化され、性能も最大で14MIPSまで向上した。ただNS-1はTS-1の各ボードをそのままNMOS VLSIに置き換えたような形になっており、例えばキャッシュは16KBと128KB、TLBサイズは2048エントリーと4096エントリーの2種類があるという、あまり他では見ない構成になっている。

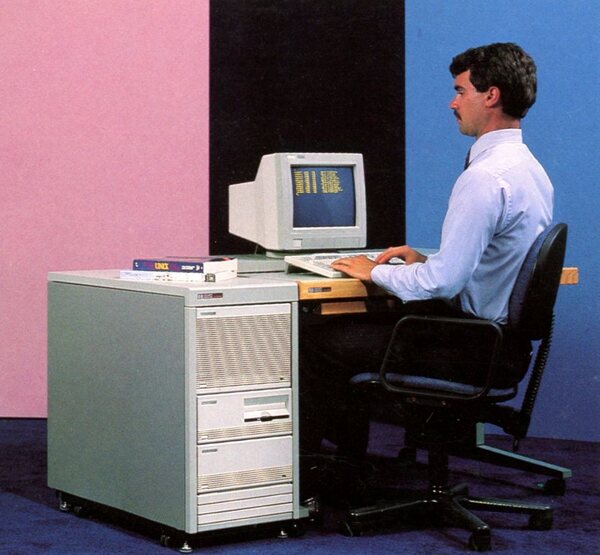

これを利用したのはHP 9000シリーズで、1987年にHP 9000/825S・835S・840Sという名前で発表され、1988年から出荷が開始されている。

画像の出典は、HP Computer Museum

このNS-1はプロセッサーバスとして32bit幅のCTB(CenTral Bus)が、I/O Busとして16bit幅のCIB(Channel I/O Bus)が用意されており、CTBはCPUボードそのものの動作周波数にあわせてバスのスピードも可変になっていた。

またCTB経由で2枚のCPUを装着することも可能で、実際デュアルプロセッサー構成の製品もカタログには掲載されていた(実際に出荷されたかは謎)。パイプラインは3段で、物理アドレスは29bit対応となっている。

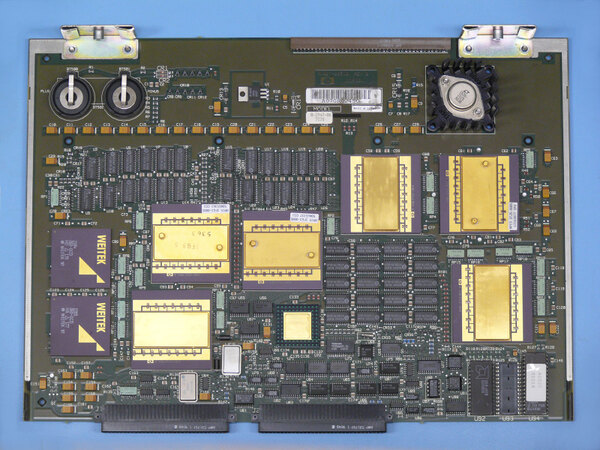

これに引き続き、1989年に開発され、1990年に製品出荷が始まったのがNS-2というチップである。

画像の出典は、Wikimedia Commons

プロセスは引き続き1μmのNMOS-IIIながらパイプラインが5段になり、またCPUボードは7チップ構成ながらオンボードキャッシュが命令/データ分離で最大1MBまで利用可能となった。

さらにTLBも最大16384エントリーまで増強されるなどしており、動作周波数そのものは最大で30MHz(製品としては27.5MHzどまり)ながら性能はやや改善している。このNS-2はHP 9000/822・832・845・855・860の各モデルで採用された。

HP 9000シリーズだけでなく、HP 3000シリーズにもNS-1/NS-2プロセッサーは採用された。1988年4月に発表され、1988~1989年に出荷されたのが、NS-1を搭載するHP 3000/925・925LX・935・955の各シリーズである。

このうちHP 3000/925・925LXは即時出荷開始、HP 9000/935は1988年末・HP 3000/955は1989年の出荷となった。

ローエンドの925と925LXは3.2MIPS、ハイエンドの955は11MIPSという性能で、その分価格も925LXで5万ドルから955で39万ドルとずいぶん開きがある。

ちなみにLXは32bitの意味で、つまり925は従来のHP 3000(Classic 3000という言い方もある)とのソフトウェア互換性があるが、925LXは新しい32bit版のみの対応という形である。

ただNS-1や後継のNS-2で、当初約束していた「HP 3000 Series 68比で互換モードでは2倍」の性能が実現できたかと言われると微妙なところで、これは次のPCXまで待つ必要があった(続く)。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ