WideIOを改良した「HMC」

発熱と消費電力が弱点

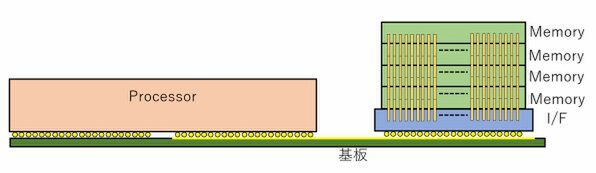

WideIOの弱点をどうするか? 次に登場したのは、「メモリーチップだけをTSVで積層しよう」という発想である。下図のように、プロセッサーとメモリーを異なる場所に配置。メモリーはTSVを使って積層し、一番下にプロセッサーとのI/Fチップを置く。

このI/Fチップとプロセッサーを高速につなぐことで、メモリーそのものは消費電力を低く抑えられ、しかも転送速度が上がると期待された。この仕組みはHMC(Hybrid Memory Cube)としてインテルとMicronが2011年に発表した。

このHMC、富士通のPrimeHPC FX100という「京コンピュータ」の民生版に採用されたので、WideIOよりはマシではあるのだが、その後は続かなかった。

後にインテルはKnights Landing(第2世代のXeon Phi)にMCDRAM(Mulch Channel DRAM)と呼ばれるメモリーを搭載したが、これはHMCをベースにした独自規格である。

HMCのなにが悪かったのか? というと、通常の基板の上でプロセッサーとメモリーを実装しようとしたことだ。HMCもメモリーそのものは512bitというきわめて広いバス幅を持つが、これをそのままプロセッサーとつなげると配線が絶望的になる。そこでI/Fチップで信号を集約する形でバス幅を減らした。

HMCの場合、信号は8対(Half-Width)と16対(Full-Width)の2種類で、信号速度は10/12.5/15Gbpsの3種類である。最小構成の8対/10Gbpsで10GB/秒、最大構成の16対/15Gbpsで30GB/秒(どちらも片方向あたり)の帯域となる計算で、WideIO以上の帯域を確保できることになる。

問題はメモリーチップの下に置かれたI/Fチップが、15Gbpsもの信号を生成するために結構発熱しており、消費電力の増加のみならず、発熱によるメモリーチップそのものへの影響が馬鹿にならなくなってきたことだ。

またメモリーとプロセッサーの両側でバス幅の変換を行なう関係でレイテンシーが増えることになり、帯域はともかくアクセス時間が延びるのもあまり好ましくないと判断された。

WideIOとHMCの利点を兼ね合わせた

「HBM」

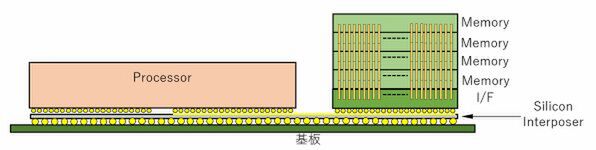

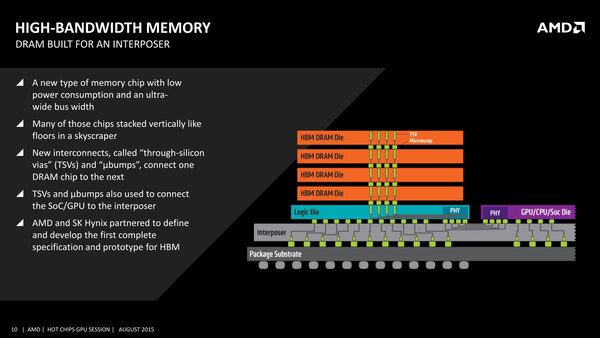

ということでいよいよHBM(High Bandwidth Memory)である。構造はHMCに似ているが、大きく異なるのは基板上でプロセッサーとメモリーをつなぐのではなく、まずプロセッサーとメモリーをSilicon Interposerという小さなサブ基板の上でつなぎ、ついでこのSilicon Interposerごと基板につなぐ、という2段階を取ることだ。

Silicon Interposerは名前の通り、半導体と同じくシリコンで生成される。このため通常の基板よりもはるかに大量の配線(技術的には1mmの間に数千本の配線を通すこともできる)が可能だ。そして、通常の基板よりも伝導特性が良いので、HMCに比べると信号の電圧/電流ともにかなり低く抑えられる。

このためHMCとは異なり、配線の際に信号を束ねる必要がなく、1024bit幅の信号線を直接プロセッサーとメモリーの間でつなぐことができる。

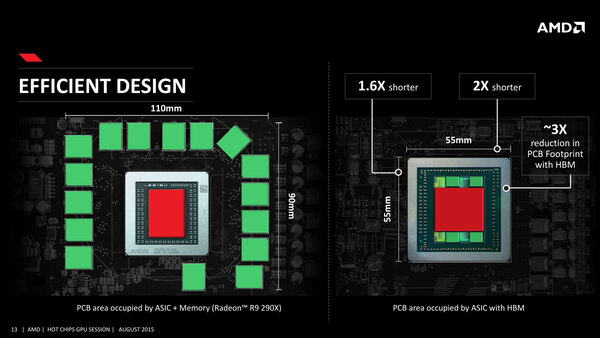

また副次的な効果として、Silicon Interposerは基板に比べてはるかに大量の配線を狭い場所に通せるので、結果として実装面積が小さくなるというメリットもある。

欠点は、新たにSilicon Interposerを必要とすることだ。この分コストが上がるのは避けられないのだが、Silicon Interposerのコストはプロセッサーの側にTSVを設けるよりははるかに低く、また実装の際のコスト(TSVではものすごく厳密に位置合わせをしないとうまく信号線がつながらない)も相対的に安いということで、WideIOの利点とHMCの利点を兼ね合わせた方式として広く普及するに至った。

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ