いよいよ、AMDの次世代CPUアーキテクチャー“Zen”を採用する初のデスクトップCPU“Summit Ridge”(サミット・リッジ、開発コードネーム)が、市場投入に向けてカウントダウン段階に入った。

AMDは、Intel Developer Forum 2016にあわせ、現地時間の8月17日に記者向け説明会を開催し、Zenアーキテクチャーの概要と製品デモを披露、Zenシリーズの開発が順調に進んでいることをアピールした。

同社を率いるLisa Su社長兼CEOは、AMDは、2016年に入って第7世代APU“Bristol Ridge”(ブリストル・リッジ、開発コードネーム)と新アーキテクチャーGPU“Polaris”(ポラリス、開発コードネーム)を投入。さらに新しいカスタムSoC契約の締結、中国において2つの共同開発案件のスタートなどのビジネス成果を得てきた。

しかし、「今年最大のトピックは、まだアナウンスされていない」として、Zenこそが今年最大のビジネス的成果になるものであり、AMDにとってはこの10年間で最高に競争力のある製品ラインナップと位置づける。

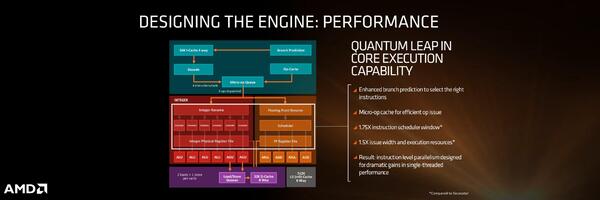

そのZenアーキテクチャーの概要については、同社で製品開発などを統括するMark Papermaster上級副社長兼CTOは、「スクラッチビルドで設計することで、クロックあたりの命令処理性能を大幅に引き上げるとともに、14mm FinFETプロセスの採用などにより省電力性を高め、ファンレスの2-in-1デバイスからデータセンター向けの高性能CPUを展開できる柔軟性を実現した」と説明。

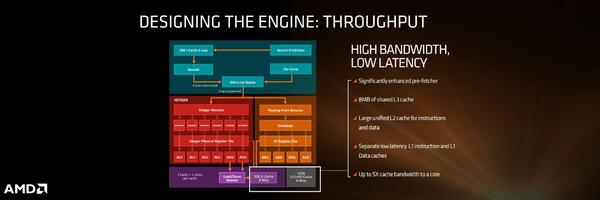

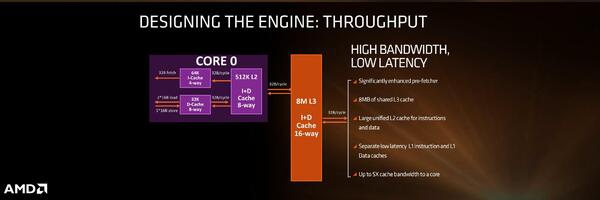

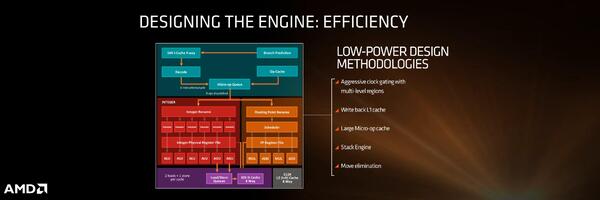

また、キャッシュ階層も新しくし、コア間でデータを共有する8MBのL3キャッシュ、各コアに命令とデータ処理で共有する512KB L2キャッシュと、64KBのL1命令キャッシュと32KBのL1データキャッシュを搭載。キャッシュとコア間は、最大5倍の転送帯域を実現することで、効率的かつ高スループット処理を実現する。

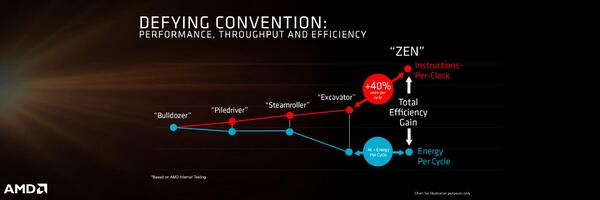

省電力効率を高めるための工夫としては、14nm FinFETプロセスの採用に加え、複数のレベルのクロック制御をよりアグレッシブにするとともに、L1キャッシュのライトバック対応、大きめのMicroOPキャッシュの採用により、クロックあたりの命令処理性能を、現行のExcavatorコアに比べて40%以上高める一方で、電力効率は同レベルに抑えていると言う。

さらにZenアーキテクチャーでは、インテルのHyperThreadingと同様の、1つのコアで2つのスレッド処理を可能にするSMT(Simultaneous Multi-Threading)をサポートする。

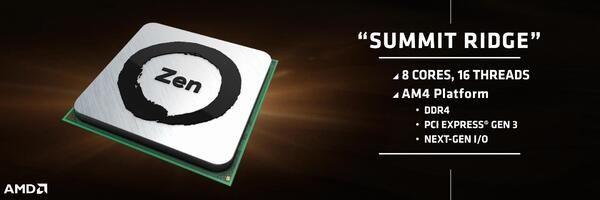

AMD初のZenアーキテクチャー採用CPUとなる“Summit Ridge”(サミット・リッジ)では、8つのコアを統合することで16スレッドの処理が可能となる。AMDは、このSummit Ridgeを年内に出荷を開始し、2017年初には、主要パートナーから搭載システムが市場に投入される見通しだ。

Summit Ridgeのプラットフォームには、第7世代APUの“Bristol Ridge”と共通のAM4プラットフォームを採用。同プラットフォームでは、DDR4メモリの対応に加え、SATA ExpressやNVMe対応が果たされるほか、USB 3.1 Gen.2もサポートすることが明らかにされた。ただし、同プラットフォーム用チップセットの詳細などについては明らかにされなかった。

AMDでは、さらにZenアーキテクチャーを2017年第2四半期にはサーバー市場に、2017年後半にはZenアーキテクチャーを採用する次世代APUを投入するとともに、組み込み市場向けにもZenアーキテクチャーを拡大していく意向を示す。

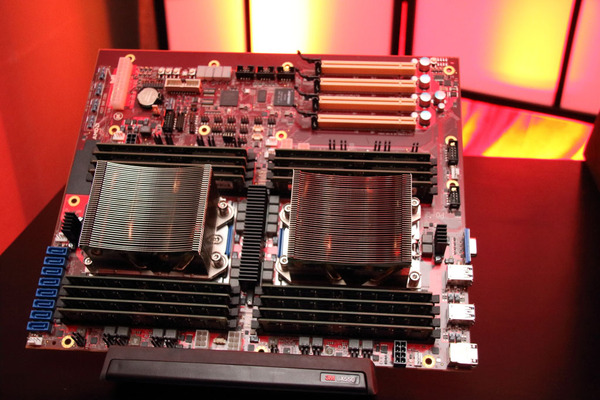

このうち、サーバー市場向け製品としては、36コア/64スレッドの2way SoCの“Naples”(ネープルス)と、その2wayプラットフォームも公開。収益性の高いサーバー・データセンター市場へ、積極的に製品展開を図っていく。なお、Zenアーキテクチャーの詳細については、8月21~23日にカリフォルニア州クパティーノで開催される「HotChip 28」で公開される予定だ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります