今回のスーパーコンピューターの系譜で取り上げるのは、英Meiko Scientificである。同社の創立は1985年のこと。創立した6人はいずれも英INMOSからのスピンアウト組である。

Meiko Scientificの超並列マシン「Meiko CS-2」

INMOSは1984年に最初のT414をリリース、その後T800の開発を始めるが、このT800の投入は最終的に1987年まで遅れた。このT800の遅れを我慢できなかった(?)メンバーが独立して、超並列構成の製品を作るべく立ち上げたのがMeiko Scientificである。ちなみに“Meiko”は女性名ではなく、日本語の“名工”に由来するらしい。

Meiko Scientificが採用したCPU

Transputer

INMOSが開発したマイクロプロセッサーアーキテクチャーのTransputerそのものは、327回にも取り上げたので、おなじみの製品である。

やや話が脇道にそれるが、もともとTransputerは、ある意味超並列のような発想で生まれた製品である。つまり、プロセッサー単体の性能を上げるよりも、多くのプロセッサーを多数接続することでトータル性能を上げようというものである。

そのため、簡単にプロセッサー同士を接続する配慮が当初から盛り込まれた。その最大のものがプロセッサー間リンクである。これは非常に柔軟で、簡単にプロセッサーを組み合わせられるもの(なにせつなぐだけ)だった。

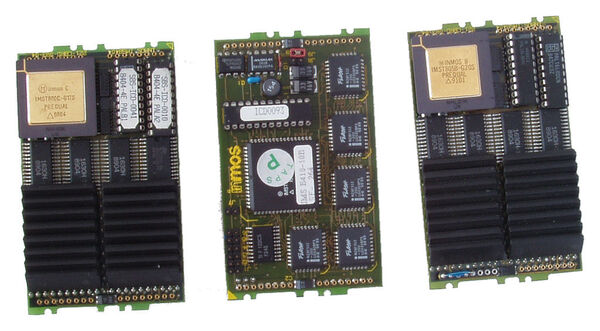

TransputerはTRAM(Transputer Module)という開発ボードを多数提供したが、このTRAM同士を後追いでケーブルでつなぐだけで連携して動くようになった。こうした使い方ができるプロセッサーは他には見当たらない。

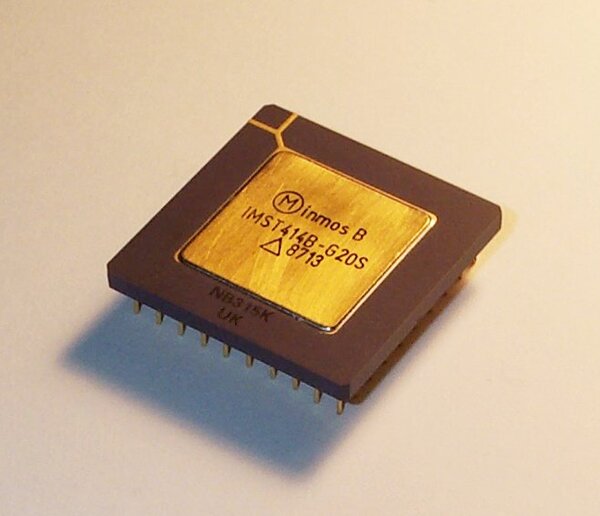

TransputerのアーキテクチャーそのものはCISCで、命令セットも単純だった。当初リリースされたT414は1.5μm CMOSで設計され、動作周波数は15~20MHz、性能は7.5~10MIPSということで、今から見ればそう高いものではないが、この当時としてはかなりパワフルな部類に入った。

もちろん絶対性能で言えばT414の後に登場したi386DXは絶対性能こそもっと高かったが、マルチプロセッサーへの配慮はなかったため、システム的にTransputerの方がより高い性能を出せる可能性があった。

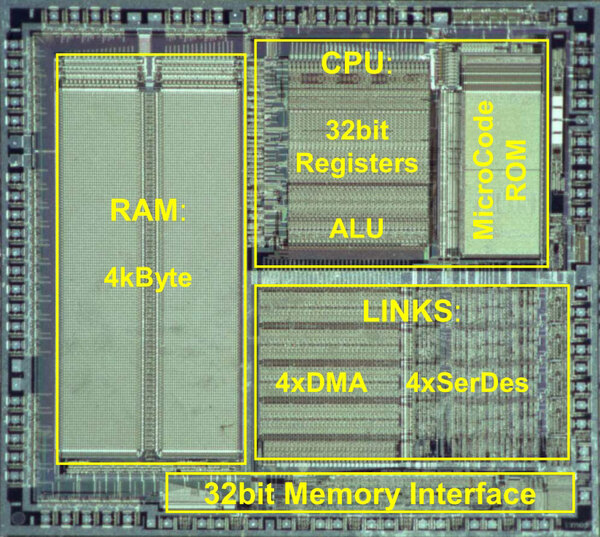

ただスーパーコンピューターで使おうとすると、浮動小数点演算は欠かせない。ところがT400シリーズの世代にFPUまで盛り込むのはダイサイズに無理があった。下の画像はT414のダイ写真だが、この時点ダイサイズは8.5×8.3mmで70.55mm2とかなり大きかった。

仮にFPUを統合したら100mm2では効かず、かなりコストアップになったであろう。しかもこのT414、上の画像を見るとSRAMが4KBあるように見える(というか、実際あった)のだがバグがあってこのうち2KBしか使えなかったというおまけ付きである。

FPUを入れてさらに大型化したら、どの程度のトラブルが出たのか、想像したくない。サードパーティーから、TRAMの上にFPU(確かWeitekのどれかのFPUだったと思うが、もう型番を覚えていない)を搭載して、浮動小数点演算を可能にするといった解決策が出ていた記憶もあるが、このあたりがきちんと対応したのは1987年(量産は1988年に入ってから)のT800以降となる。

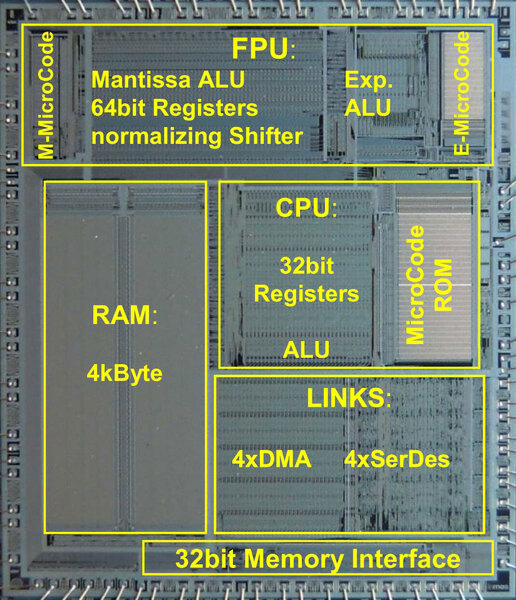

T800ではプロセスは同じながら、20MHz駆動で20MIPSと性能は倍増したうえ、64bitの浮動小数点演算が可能なFPUも搭載された。当初はこの製品を1985年にリリース予定だったが、開発が難航して2年ほど遅れたことになる。もっとも2年遅らせただけのことはあって、完成度はずっと高まっていた。

ちなみにFPUを搭載したといっても、このサイズではパイプライン化したものは入れられず、性能は20MHz駆動で2.8MFLOPSどまりとなっていた。もっともこれだって、この当時からすればかなり高速である。

同列で比較してはいけないのだが、翌年登場したインテルの80486DX-25MHzのLinpackのスコアは1MFLOPSとされている。当時はインテルもまだパイプライン化したFPUは搭載していなかったからだ。

T800のLinpackのスコアは、オークリッジ国立研究所が25MHz駆動のT800で0.32MFLOPSを実現したという記述は発見したが、元の論文が見つかっていないので正しいかどうかはわからない。ただ、性能を考えればそんなものだろう。

→次のページヘ続く (Meiko Scientific初のマシン「CS-1」)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ