今回はいつものロードマップをお休みして番外編となる。先週筆者は諸般の事情でロンドンに滞在していた。主にロンドンのScience Museumにいたのだが、ここの2階に“Information Age”と呼ばれるエリアがあり、木の棒を叩いて通信していた時代から電信・電話を経てコンピューター世代までの200年以上の歴史がまとめて展示されていた。

このInformation Ageの中に、いろいろおもしろい展示があったので、今回はそれを写真でご紹介したい。

ロンドンにあるサイエンス・ミュージアム

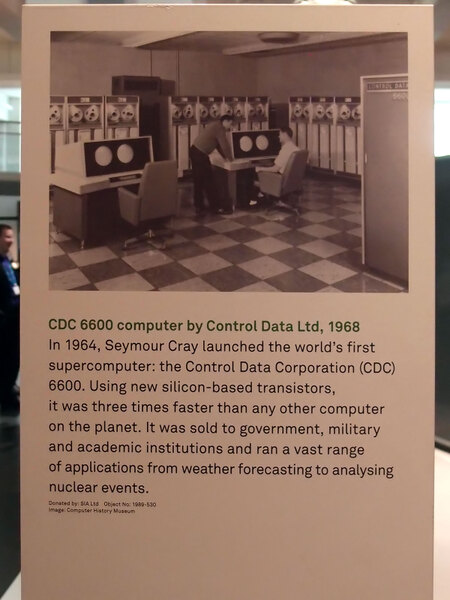

CDC 6600

連載273回で解説したCDC 6600の実機が展示されていた。高さそのものはオフィスのパーティションくらいで、ただしPhoto01の写真でもわかる通り厚みはそれなり。

上から見ると4つのキャビネットを十文字型にユニットを組み合わせている模様だが、展示されていたのは2キャビネットのみ。木目調のコンソール(Photo05)がいい味を出している。CRTは2つの丸型ブラウン管を横に並べた形なのもわかる。

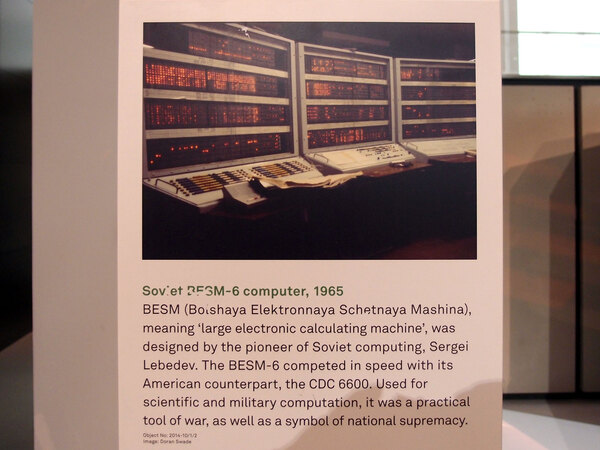

BESM-6

1960年当時の西側諸国のハイエンドがCDC 6600だとすれば、東側諸国のハイエンドがこのBESM-6だ。

BESMはBESM-1~BESM-6があり(ただしBESM-5だけは聞いたことがないので、スキップしたのかもしれない)、BESM-6は全体で1MFLOPS程度を出す、当時としてはハイエンドのスーパーコンピューターであった。

モスクワ大学のスーターコンピューテイング・センターのヒストリーページを見ると、当時の状況が説明されている。

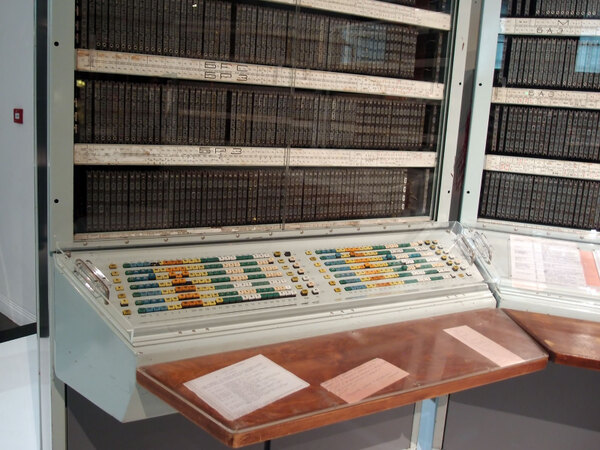

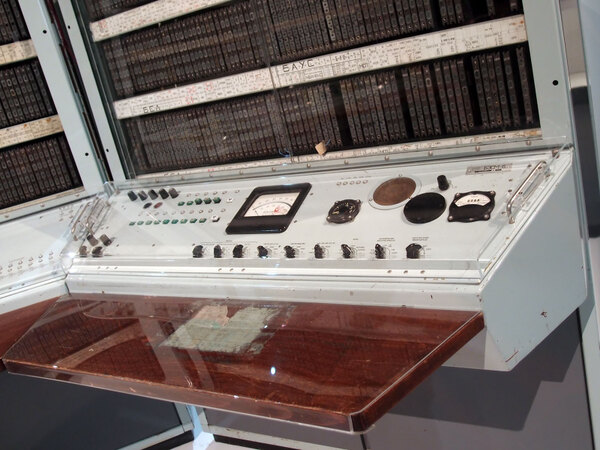

それにしても、操作パネルを見ると、コンピューターというよりはなにか工場の制御装置という感じもする(特にPhoto11)。コンソールの上のガラス張りのラックの中のモジュールは動作状態に応じて細かく点灯するようで、Photo12でみるとモジュールあたり8つのランプが装着されているのがわかる。

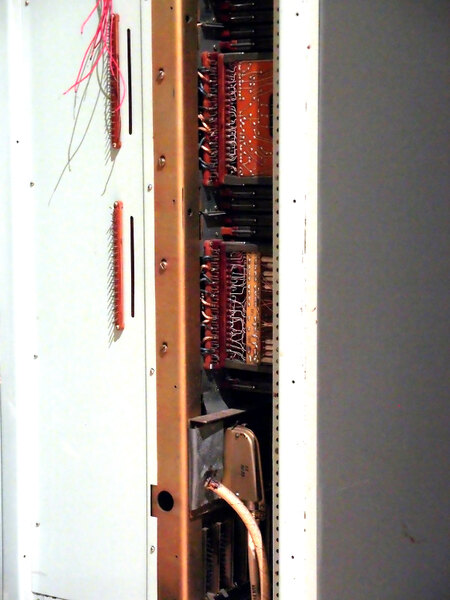

Photo13~15は、BEMS-6の側面を撮影したが、Photo13が上部で、モジュール用の配線が4段分用意されているPhoto14が真ん中あたりで、モジュールへの電源供給配線だろうか? Photo15が最下部で、こちらは明らかに電源配線(それも結構高圧っぽい)である。

→次のページヘ続く (米軍の防空システムなど)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ