CPUアーキテクチャーの進化

CPU高速化の常套手段 パイプライン処理の基本 【その1】

2010年09月06日 12時00分更新

パイプライン処理の基本

ステージごとに次々と処理させる

以上の基礎知識を踏まえた上で、もう少しCPU内部の話をする。一般にCPUの場合、行なう処理は次の5段階(ステージと呼ぶ)からなる。

- Fetch

- 次に処理すべき命令を、メモリーやキャッシュから取得する。

- Decode

- 取得した命令を解釈し、どんな処理を実行すべきかを決定する。

- Data Fetch

- 必要なら、処理に必要なデータを取り込む。

- Execute

- 処理する。

- Writeback

- 処理結果を出力。

古いCPUでは、DecodeとData Fetchが一緒になって4ステージとか、ExecuteとWritebackを一緒にして3ステージとか、FetchとDecodeも一緒にして2ステージとか、いくらでも簡単にはできるのだが、機能で分割すればおおむねこの5ステージとなる。

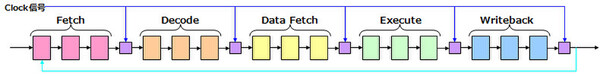

そしてこれらを実装する場合、内部回路は大雑把に図4のようになる。上の5つのステージはそれぞれ、複数の回路をつなげる形で実装されている。基本的には、Writebackの最終処理が終わったら、それをトリガーに次の命令のFetchを開始するような仕組みだ。

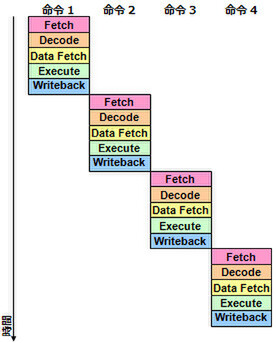

そして図4の場合、どのように命令が処理されてゆくかを示したのが図5である。ここではとりあえず、5つのステージがいずれも同じ時間で処理できるという前提にしているが、仮に1ステージ1クロックで処理できるとしても、1命令あたり5クロックを要することになる。図のように4命令実行なら、20クロック必要になる計算だ。

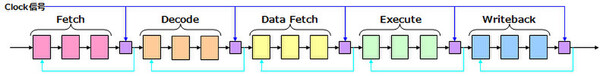

これを「もう少し高速化できないか?」ということで考えられたのが、パイプライン処理である。基本的な構造は変わらないが、これまでは「Writebackの出力が終わったら次のFetchを開始する」だったのが、「各ステージごとに、処理が終わったら次の命令の処理を始める」形に変更されている(図6)。

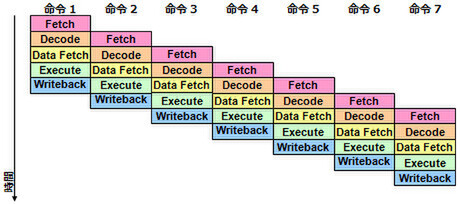

これを実行した場合、処理の進み方は図7のようになる。

各々のステージに要する時間は変わらないが、各ステージが常に処理を行なっているため、実質的な処理能力が(この図の場合)5倍になっているわけだ。こうした形で、常にCPUの内部回路全体が動作するようにしたものが、パイプラインと呼ばれる高速手法である。

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ