アスペクト比5:1の衝撃! Ru配線が実現する「究極の低抵抗」

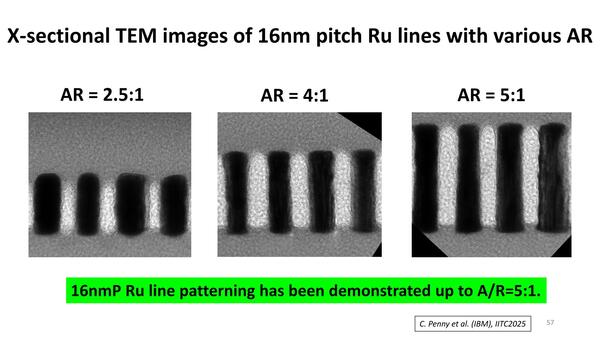

TiNを利用するとLine Wigglingの影響を最小限に抑えて配線が構築できることはわかったが、では配線をどの程度の高さにできるのか、というのが次の話である。

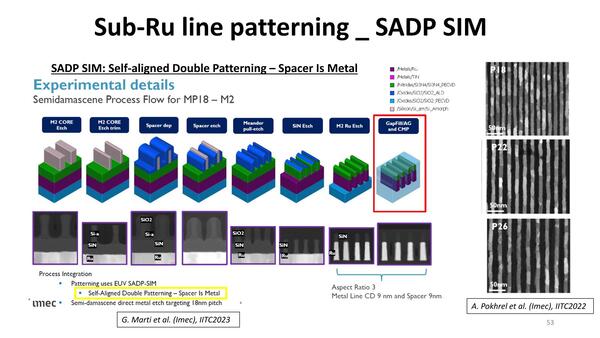

高さを稼ごうとすると、比較的簡単なのはSADPを使って製造することになる。もちろんRu配線が利用されるのはトランジスタ層に比較的近いM0~M3あたりまでなので、SADPが利用されるのはごく普通である。

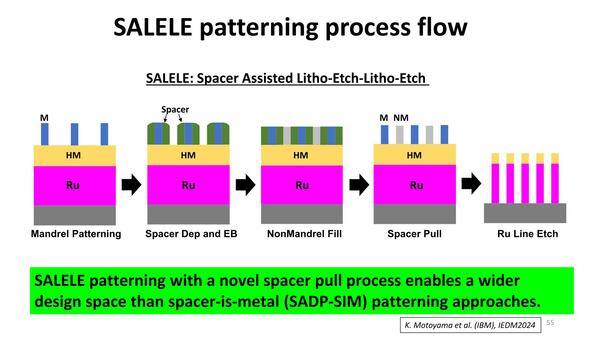

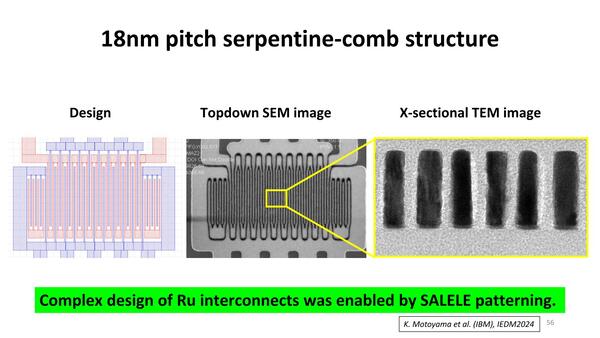

ただ、さらにアスペクト比を上げる方法としてSALELEも提案されている。このSALELEを利用することで、高アスペクト比のRu配線が実現できる、としている。

実際16nmピッチのまま、アスペクト比を5:1まで構築できることが示されており、性能を優先するならこの手法はかなり現実的である。

アスペクト比を5:1まで構築できる。あるいは将来Ru配線が実用化される時代になると、アスペクト比3と5の両方の配線方法がオプションで用意されるのかもしれない。LELEをやる時点で、配線層の構築コストがSADPの倍くらいになるからだ。性能を取るか、コストを取るかという話になりそうだ

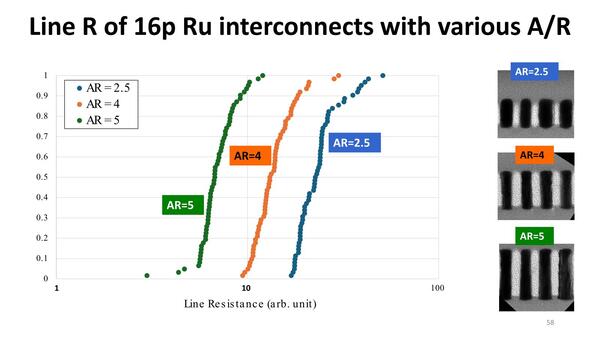

配線抵抗そのものは確実にアスペクト比2.5や4に比べて5の方が下がっていることが示されており、性能的には優秀だからだ。

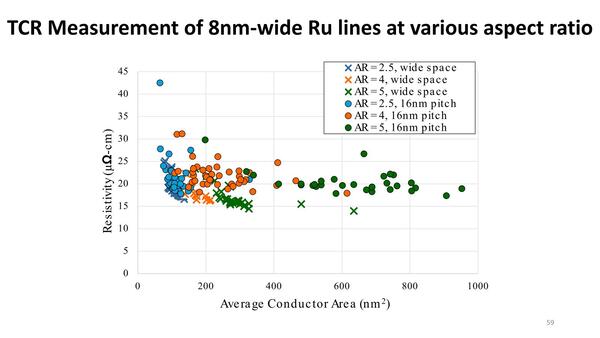

下の画像は実際の抵抗値と面積を比較したもので、アスペクト比5が一番優秀な数字になっている。

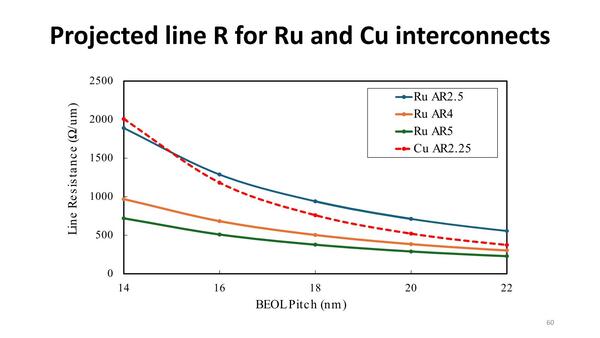

もう1つおもしろいのは、配線ピッチと抵抗の関係。ここまでは16nmの話をしてきたが、銅配線は20nmを切ったあたりから急速に抵抗値が増えるのに対し、Ruでは抵抗値そのものも低いし、上がりかたも緩やかであることがわかる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ