コアの数だけMMAが搭載されるためAI処理が高速になった

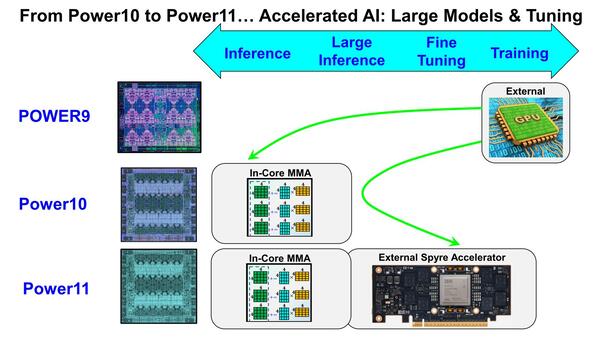

AI性能に関しての改良がIn-Core MMA(Matrix Math Accelerator)とSpyre(スパイア)アクセラレーターの接続である。Spyreアクセラレーターに関しては連載790回でも説明したが、もともとはTelum IIとあわせて発表されたPCIeカード型のAI推論用アクセラレーターである。

Telum IIと同時に発表されたからといってz専用ではなくPower11でも利用できるという話として、MMAの方はPOWER10時代に実装されたものである。

例えばMMAの性能が今回POWER10世代から倍増したわけではないようで、単にコア数がSKUによっては増えたことと、動作周波数が上がったこと、それとメモリー容量/帯域が増えたことで、従来よりAI処理が高速になったというだけのようだ

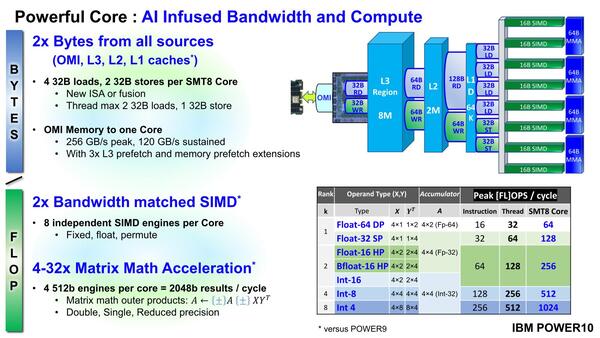

構造としてはインテルのAMXやArmのSME2と同じく、行列演算を一気に行なえるようにしたものであるが、AMXはアクセラレーターの形でソケットに1つだけ搭載されるし、SME2はコアクラスターあたり1つ(次世代は2つになるらしい)だけの搭載なのに対し、MMAはこれがコアの数だけ搭載されるわけで、下手な専用アクセラレーターよりも高速に処理できるかもしれない。

ここまででわかるように、POWER10からPower11への変更はあまり多くない。製造プロセスがあまり変わらないあたりが、マイナーアップデートの域を出ないことが示唆されている。メモリー周りの大幅強化で実効性能そのものは明確に上がっているかもしれないが、やや行き詰まり感がある。

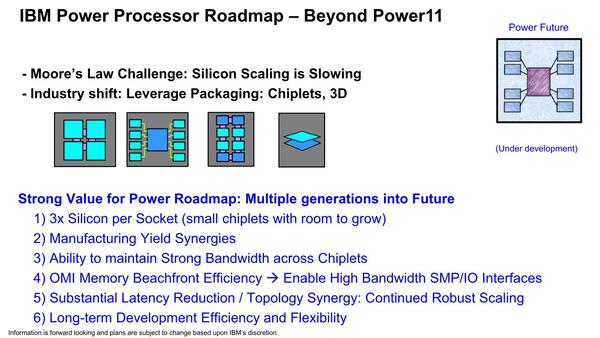

そうしたことを踏まえてか、将来計画ではチップレット化による、より大量のシリコンの実装や歩留まりの向上、OMIの効率化などが示されている。

もっともzシリーズに比べると更新頻度がゆっくりなPowerシリーズなだけに、次の製品が出てくるのは2028年か2029年になるかもしれない。その頃だと製造プロセスは2nmを切ってるというあたりか? そろそろPowerとzの製品ライン統合があっても不思議ではない状況だが、本当にPower Futureは出てくるのだろうか?

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ