ロードマップでわかる!当世プロセッサー事情 第843回

NVIDIAとインテルの協業発表によりGB10のCPUをx86に置き換えた新世代AIチップが登場する?

2025年09月29日 12時00分更新

消費電力はGB10全体で140W

動作周波数をB200の3分の1くらいに落とさないと不可能な数字

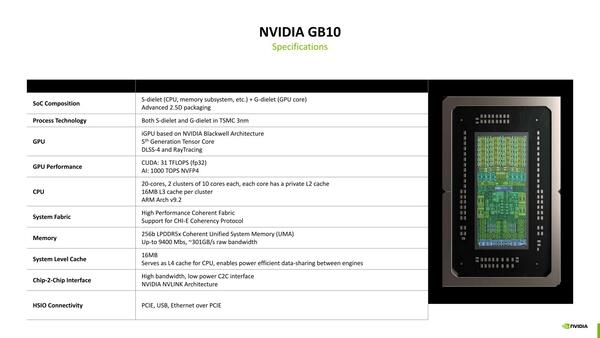

下の画像がGB10そのもののスペックである。まずGPU Dieletであるが、写真で言えば上側にあたる部分だ。動作周波数などは不明だが、AI向けがFP4で1000TOPS(1peta OPS)であり、FP32を使ったCUDAの場合で31TFlopsとされる。

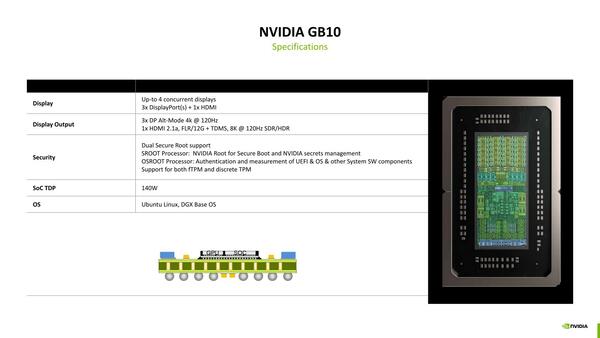

HDMI以外にDisplayPort×3が追加されている。DGX Base OSというのはUbuntuの上にNVIDIAがDGX用のソフトを載せたもので、最新はUbuntu 24.04をベースにしたDGX OS 7となる

まずAIの方で見ると、この1peta OPSというのは、GB200 NVL72に搭載されるB200のちょうど20分の1の計算になる。記事冒頭の画像で示されるように、B200はGPCあたり20個のTPCを搭載、TPCあたりのSMが2つである。そのGPCがダイあたり4つなのでダイあたり80TPC、160SM。2ダイで160TPC、320SMという計算になる。

SMあたりのCUDAコアは128なので、40960 CUDAコアという計算だ(冗長ブロックは勘定に入れずに、理論上の個数を計算している)。一方、上の画像を見ると、TPCがトータルで24個あるように見える。したがって数だけ計算すると24:160≒1:6.67ということで、TPCの個数とはマッチしないのだが、おそらくそれだけ動作周波数が落とされているものと考えられる。

NVL72に搭載されるB200はTDPが最大1200Wという代物で、とうていDGX Spark Workstationの筐体では冷却能力が不足している。後述するが消費電力はGB10全体で140Wと説明されており、CPUも相応に電力を喰うし、メモリーコントローラーその他もあることを考えると、GPUが消費可能な電力は良くて100W程度だろう。これに収めようとすると、動作周波数をB200の3分の1くらいに落とさないと辻褄が合わない。

B200は2ダイで1200Wなので1ダイで600W。動作周波数を3分の1にすれば、消費電力が100Wくらいまで落ちることそのものは不思議ではない。加えて言えば、製造プロセスはGB200などのTSMC 4NからTSMC N3に変更になっている。この分も多少は省電力化に貢献しているかもしれない。

CPUもやや珍しい構成である。20コアだが片方はCortex-A925×10、もう片方がCortex-A725×10となっている。高効率なCortex-A520ではなく、バランス型であるミドルレンジのCortex-A725を選んでいるというあたりで所謂big.LITTLE的な狙いでないことは明らかだし、クラスターごとに独立した3次キャッシュを16MB搭載するというのも使い方として珍しい。

おそらくCortex-A925のクラスターがBlackwellとのデータのやり取りや実行制御、Cortex-A725のクラスターがOSやその他のI/Fとの制御などを担当するのではないかと思われる。2つのクラスターがそれぞれ独自に16MBの3次キャッシュを持っているということは、10コアずつ別々にDynamIQのクラスターが搭載され、間がCache CoherentなSystem Fabricでつながる構造になっているはずだ。

興味深いのは、System FabricがCHI-Eをサポートしており、またCPUとGPUの間はNVLink C2C I/Fで接続されていることである。なので、実質的には連載838回で紹介したNVLink Fusionをサポートすることが可能ではないかと思われることだ(まだGB10発表時点ではNVLink Fusionの発表が行われていなかったのと、NVLink Fusionの外部への公式の実装はRubin世代になると思われていたから、BlackwellベースのGB10は微妙にこの条件から外れることになる)。

もっともNVLink FusionはこのGB10をベースに開発されたのではないか? と思う節もある。C2C周りはNVIDIAの独自IPとはされているものの、実際にはUCIeのIPの上にNVIDIAのNVLink用のプロトコル層を載せたのではないか? と考えるからだ。

LPDDR5は256b幅で128GBとあるから、あるいは2024年7月にSamsungが発表した16GBのLPDDR5xあたりが使われている可能性が高い。おのおの32bit幅で8個搭載すると256bit幅・128GBとなる。

上の画像では、最大4枚のディスプレーが接続できることのほかにSoC TDPが140W(*)であることが示されている。CPUとGPUはどちらもインターポーザー(おそらくらくシリコンでCoWoSを利用している)に搭載されているのがわかる。

(*):NVIDIAの仕様ページではPower Consumptionが"TBD(To Be Determined:後で発表)"になっている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ