COUPEの中身が初公開

SoIC-Xで“光化”爆進!

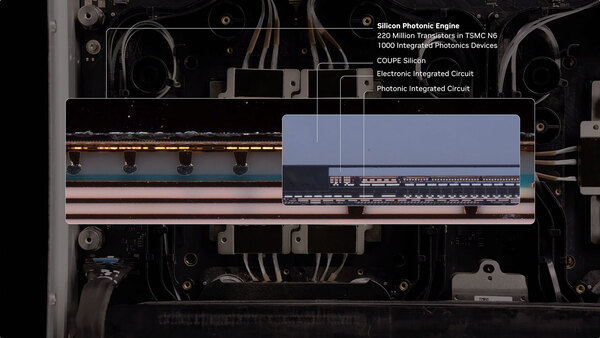

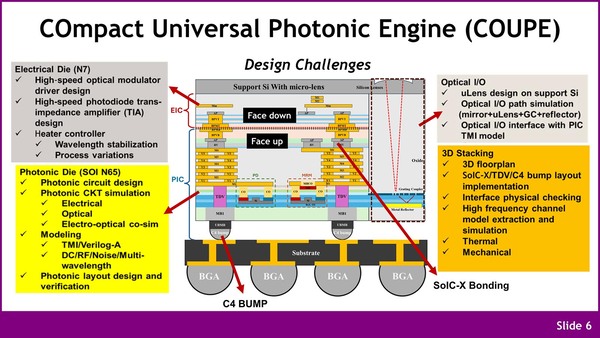

そのCOUPEの中身として初公開されたのが下の画像である。PICとEICを縦積みした構造であるが、PICが下側に配されるので、まずPICからTSVを使って信号をEICに送り、そこからPICに信号が渡されるという構造になっている。

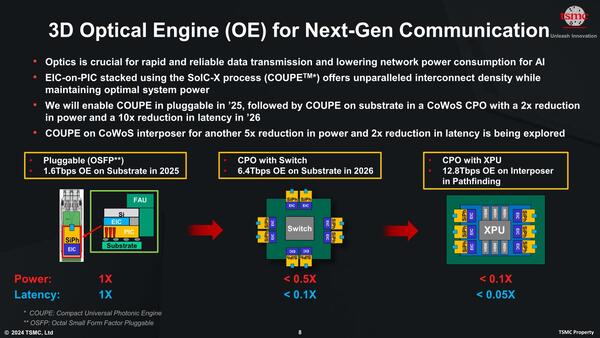

ちなみにこれは第1世代のCOUPEであるが、この先2世代にわたって進化し、最終的には消費電力を現在の10分の1、レイテンシー20分の1にできるとしている。

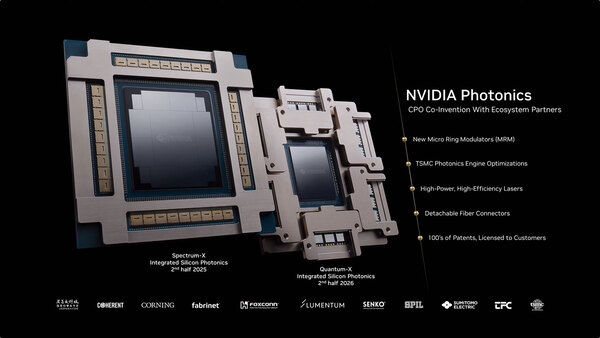

第1世代のCOUPEは、2025年3月に開催されたGTCの基調講演の中で、同社のイーサネット・スイッチのSpectrum-Xとインフィニバンド・スイッチのQuantum-XにこのCOUPEが採用されることが明らかにされている。

さてやっとVLSIシンポジウムに話が戻ってくるわけだが、今回セッションの中でこのCOUPEの内部構造が明らかにされた。

Modulator(MRM:Micro Rind Modulator)やPD(Photo Detector)はPICのダイの真ん中辺にあるあたり、送受光部(右端)まではSiなりSiNでの導光路を形成するのだろう

EICはN7プロセスで製造され、TIA(Trans Inpedance Amp)や、OCI側のModulationの制御用ヒーターコントローラー(Ring Modulatorは温度による影響が大きいので、温度管理が必須となる)などが実装されている。一方PICは光信号の送受信などの回路が実装されている。

特徴的なのは、このEICとPICがSoIC-X(microbumpを使わない、直接接続の3次元実装。AMDの3D V-Cacheと同じ方式)を利用していることである。ほかのメーカーのCPOには見られない特徴として、送受光部はPICの位置にあり、そこからおそらくミラーを利用して垂直方向に曲げ、さらに(オプション扱いのようだが)Micro Lensの実装も可能となっている。

SoIC-XでEICとPICを接合しているというのは、もう同社のSoIC-Xの製造工程そのままでCOUPEを構築できるということで、もちろんSoIC-Xの製造コストはやや高めではあるものの、実績のあるプロセスということで製造にまつわる問題はそう多くないものと考えられる。

またSoIC-Xだと最短経路で接続を構築できるし、接続部の抵抗や寄生容量もMicroBumpに比べるとかなり小さくなっているので、性能への影響が低いというPhoto03のグラフも納得だし、垂直接続なのでEICとPICの配線長は最小限に抑えられ、おまけに抵抗と寄生容量が低ければ消費電力が下がるのも当然である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ