VLSIシンポジウムの2日目は、Short Courseと呼ばれる「初心者向け」のセッションが設けられている。ここでの初心者というのは、「その分野は知らないけど、基本はプロ」の意味である。例えばアナログ回路の設計や実装をやっている人に昨今のチップレットの動向を紹介するなど、そういう感じの話であって、本当の意味での初心者向けではない。

そのShort Courseは6月9日の8時25分から17時25分(Course 1は16時35分まで)、ぶっ続けで8~9テーマの説明をするというなかなかヘビーなものである。コースは2つあり、これが同時並行で進んでいくわけだが、タイトルを並べると以下のとおり、かなりヘビーな内容である。

| Short Course 1(Key VLSI Technologies in the AI era) | ||||||

|---|---|---|---|---|---|---|

| ・CMOS Scaling Exploration: Technology Trends and System-Level Perspectives ・2D Materials and Their Application Space - Recent Insights Gained - ・Heterogenous System Partitioning, the 2.5D and 3D Integration Landscape and Roadmap ・Etch and Materials Innovations for Advanced Logic and Memory Applications ・DRAM History and Challenges ・Current Landscape and Future Outlook of Emerging Memory Technologies ・DTCO/STCO for Multi-Objective Optimization from Device to System ・Heterogeneous Integration Technologies for 3D Integrated CMOS Image Sensors |

||||||

| Short Course 2(Circuits and Systems for AI and Computing) | ||||||

| ・Hardware Accelerator Design for AI: Enabling Efficient Generative Models ・Architecture Trends for AI Hardware Platforms ・Modular Chiplet Approaches for Scalable and Efficient Machine Learning ・AI for EDA: Challenges and Opportunities ・Connectivity Technologies to Accelerate AI ・3D Optical Interconnect Design ・HBM for AI Computing ・Semiconductor Storage for Further Evolution of Generative AI ・Advancements in Power Architectures for AI Computing ・Hybrid Power Systems |

||||||

電気信号から光信号に変換しないと効率が悪すぎる

今回はこのShort Course 2の"3D Optical Interconnect Design"(TSMCのF.Lee博士)からいくつかスライドを流用して、TSMCのCOUPE(COmpact Universal Photonic Engine)について説明したい。

このセッションそのものはあくまでも昨今のSilicon Opticsを利用したCPO(Co-Package Optics)に必要となる光学部品の要素について、その動作原理や特徴、実装時の注意などを細かく説明したものであってCOUPEそのものの紹介ではないのだが、いくつかCOUPEと関係ある、しかも初出のスライドも多かったので、こちらを利用してCOUPEを説明する。

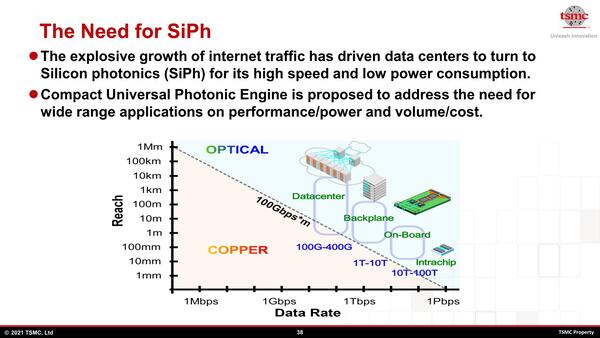

COUPEの名前が初めて登場したのは、2021年に開催されたHot Chips 33のTutorial Sessionである"TSMC Packaging Technologies for Chiplets and 3D"の中である。COUPEは要するに電気信号と光信号のコンバーターであって、これまで電気信号ベースでやり取りしていた配線を光信号に変換するにあたり、その配線の両端に入れる形のものだ。なぜ電気配線のままではまずいか? は下の画像をご覧いただきたい。

前回のGlobalFoundriesのスライドの方が現実的ではあるのだが、直感的にはこちらの方がわかりやすいかもしれない

要するに転送速度×到達距離を考えた場合、100Gbps・mが1つのしきい値であり、これを超えると電気配線では著しく効率が悪化するので光信号に切り替えたい、という話である。このコンバーターも相応に消費電力が必要なのだが、それを加味しても電気信号から光信号に変換しないと効率が悪すぎるのだ。ここは前回も少し触れたことだ。

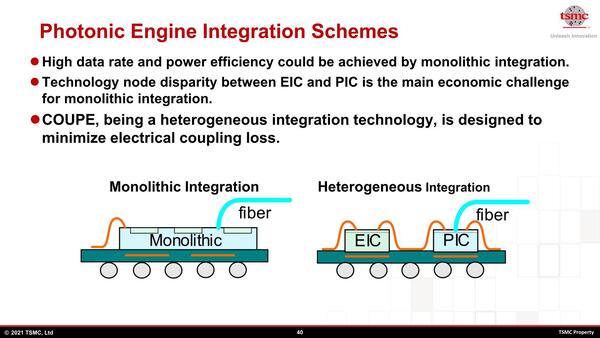

さて、そのコンバーター、電気信号を受ける部分をEIC(Electric IC)、光信号を受ける部分をPIC(Photonic IC)と呼ぶが、これを一体で作るか、別体にするかである。

FotonixはRF SOI CMOSプロセスを利用し、SiGeの高速動作トランジスタを利用することでプロセスノードの大きさ(第1世代は90nm、第2世代は45nm)に起因する遅さをカバーしているが、ロジック密度の低さはどうにもならない点が問題ではある。いろいろやらせなければいいのだが

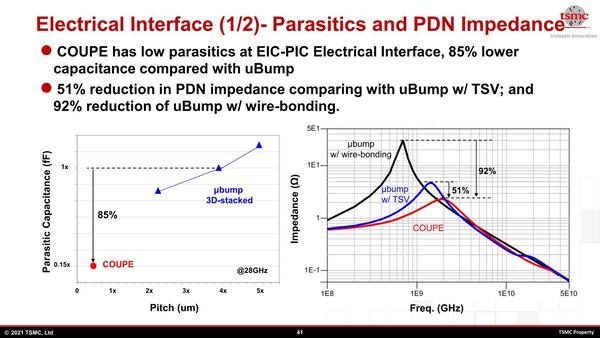

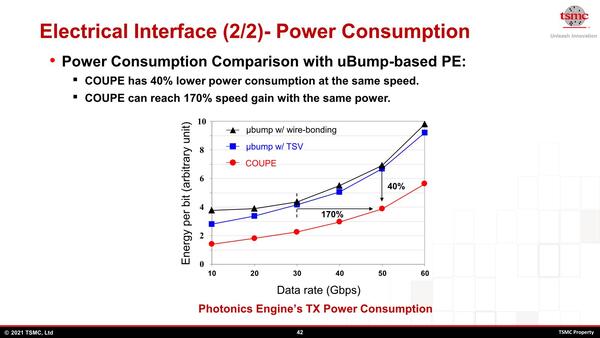

今のところこれを一体で作れるのはGlobalfoundriesのFotonixだけであって、普通は別体にせざるを得ない。COUPEも別体というか別ダイで作らざるを得ないのだが、問題はこのEICとPICの間の接続である。上の画像のように2つのダイを別々に配して間をWire Bondingでつないだ場合、TSV+Microbump(いわゆるインターポーザーを使う構成)の場合、それとCOUPEの3つのパターンを考えて、2つのダイの間の配線の抵抗と容量を比較すると、とにかく配線抵抗も寄生容量も大きくなるのが問題である。

なにせPICとEICの間は、最終的な光信号と同じ速度の電気信号が流れる。光ファイバーで100Gbpsで通信するものだとすると、ここもやはり100Gbpsになるので、寄生容量と抵抗は非常に大きな問題になる。これをCOUPEを使うことで解決できるというわけだ。またCOUPEにすることで、このコンバーター全体の消費電力も減らせるとしている。

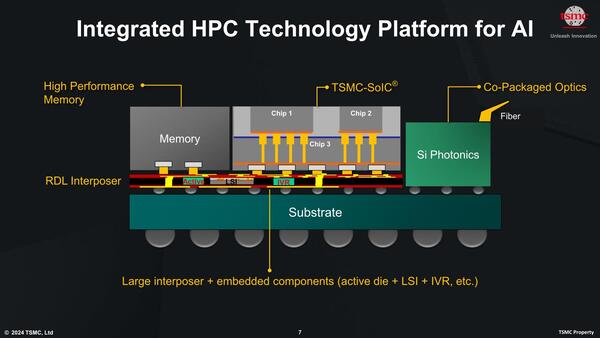

などと説明はあったものの、2021年のこの時点ではCOUPEの構造は一切公開されていない。これが公開されたのは2024年のTSMC Technology Symposiumである。下の画像は将来のAIプロセッサーの構造の模式図であるが、このSubstrateの上に載っている一番右の"SI Photonics"と呼ばれる部分がCOUPEである。

この連載の記事

-

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 - この連載の一覧へ