ロードマップでわかる!当世プロセッサー事情 第832回

Intel 18AでSRAMは進化したか? Synopsysが挑む最適化技術とWrite Assistの新アプローチ

2025年07月14日 12時00分更新

放電までの時間を減らすためにSynopsysが導入した新技法

Parallel Boot Injection

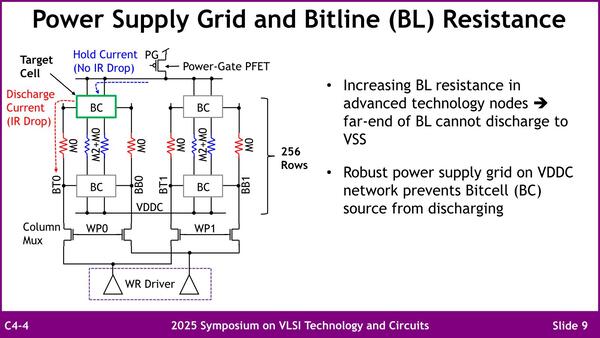

さてここからが実際のSRAMの中身についてである。下の画像は従来型のSRAMの構造である。下側にあたる2つのBCは放電の際のIRドロップが少ないのに対し、下側はM0に起因するIRドロップが大きくなる(下の画像では上と下の2組しか書かれていないが、実際にはここに256個のBCが縦に並んでいるので、256個分のM0に起因するIRドロップが発生する)関係で、放電が十分にできない問題が出てくる。

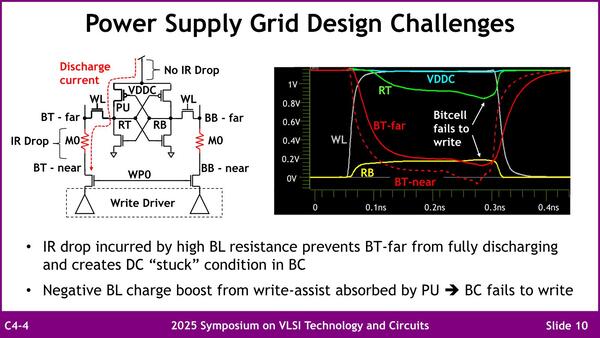

この場合の電圧ドロップの様子が下の画像に示されている。この原因は、BC同士の接続にM0とM2を併用しているせいで抵抗値が放電経路と異なるためである。

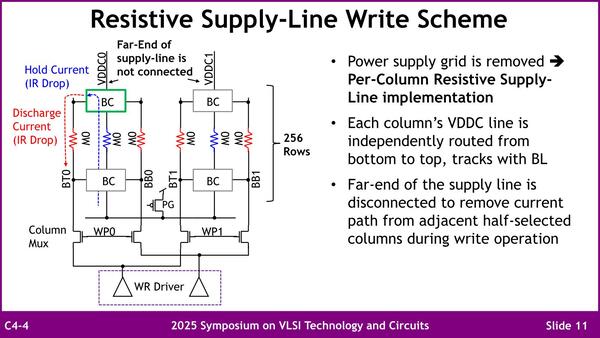

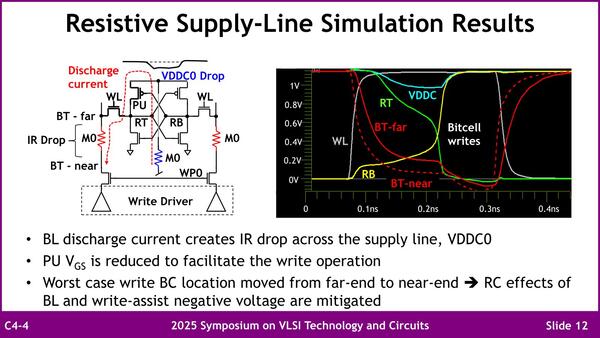

そこで、「M0のみで接続することで抵抗値を一致させる」「ホールド線(2つ上の画像では一番上に位置している)の場所を一番下にする」という2つを変更した。こうすることで、ちゃんと放電できるようになったわけだ。

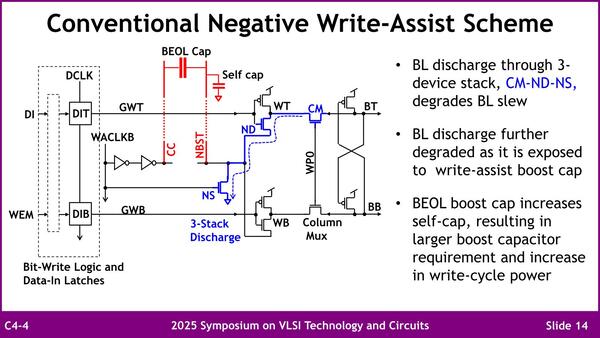

この「ちゃんと放電させる」仕組みをこれまで担保していたのがNBLの仕組みである。前頁の画像で、M2層にWA Boost Cap(Write Assist Boost Capacitor)という記述があるが、下の画像で言えばBEOL Capがこれに相当する。

M2層を利用したキャパシタはブーストキャパシタと呼ばれるが、ここに蓄えられた電荷がNSと書かれたFETのソースと結合することで、強制的にNDから電荷を引き抜くという形でNBLが動作する。これは確実に電荷を引き抜くという点では効果的なのだが、その反面CM(Column Mux)/ND/NSという3つのFETに過大な負電荷をかけてしまうことと、この放電に時間がかかる関係で遅延が生じやすいのが問題となっていた。

過大な負電荷は、ADM(Access Disturb Margin)と呼ばれる、SRAMの信頼性の指標に大きな影響を与えるもので、それもあって例えば前回も説明したようにIntel 18AのSRAMではNBL write assistがオプション扱いになっている。確実な性能を取るか、安定性を取るかという話だ。

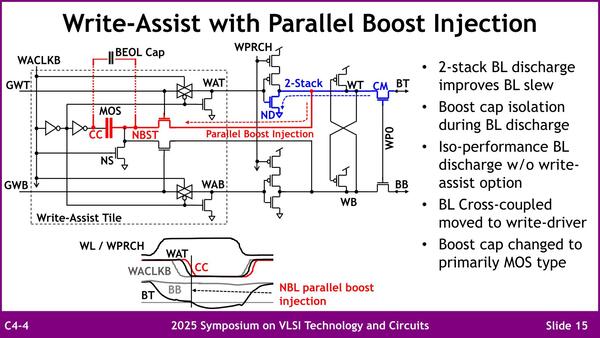

これに対してSynopsysでは新しくParallel Boot Injectionと呼ばれる技法を導入した。Bit LineはFETが2つ(2スタック)に減らされたことで放電までの時間を減らし、またキャパシタとセルの間にNBSTを挟み込み、これでキャパシタ充電の高速化およびセル放電中のBL Clampingが可能になったとする。結果的に、書き込みドライバのサイズを半分に、キャパシタのサイズも小さくでき、また漏れ電流の削減も可能になったうえ、ADMの悪化も防げるようになったとしている。

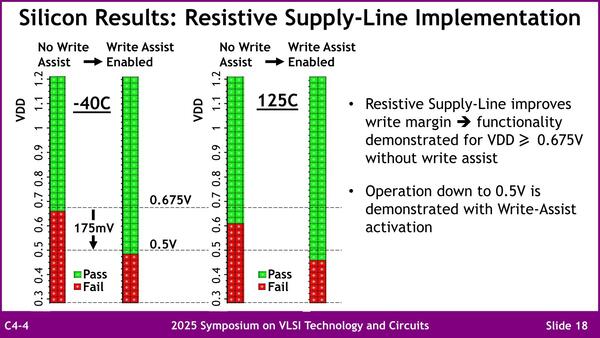

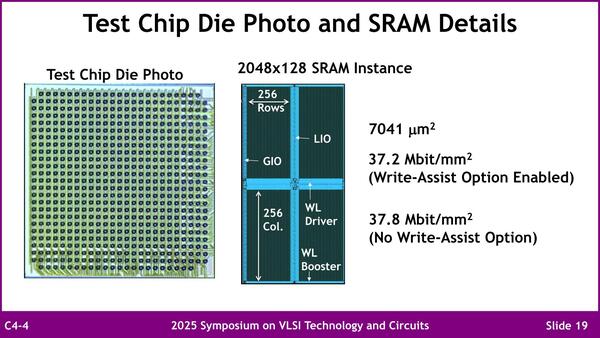

実際にIntel 18Aを利用して試作したシリコンでの動作結果が下の画像で、Write Assistなしでも0.675V以上なら、Write Assistありなら0.5V以上での動作を確認できたとしており、Write Assistなしで37.8Mbit/mm2、Write Assistありでも37.2Mbit/mm2を達成できた、としている。

左のTest Chipの細かい黒丸の中身が右の写真となる。右の方が7041μm2で2048×128bitだから37.231Mbit/mm2となる計算。Write AssistなしだとWL Boosterの面積がさらに削除できるのだろう

今回の発表内容は、SynopsysのEDAツールを使ってIntel 18Aプロセスを利用しようという顧客には良い選択肢になるように思える。ただ"small bit-count range"向けということはL2/L3向けではないことになるあたりは、使いどころが限られそうではある。高速向けではないあたり、スクラッチパッドにも向いてない気もする。なにより、Intel 18Aを使おうという顧客を見つけるのが最初の課題になるかもしれない。

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ