ロードマップでわかる!当世プロセッサー事情 第817回

実現困難と思われていたUCIe互換のチップレット間インターコネクトをTSMCとAMDが共同で発表 ISSCC 2025詳報

2025年03月31日 12時00分更新

UCIeの仕様を満たす結果を残し

不可能な数値ではないことを立証

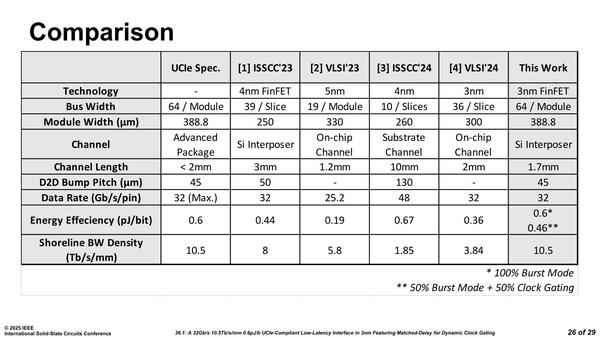

消費電力の内訳が下の画像だ。消費電力が一番大きいのは送信そのものではなく、送信側のSerDesとFFE/Deskewなどの伝達エラーを改善するための仕組みであり、次いで受信側の信号補正とDeSerとなり、送信そのものは3番目というのはなかなか興味深い。これでBurst Modeで0.6pJ/bitというUCIeの仕様を満たす結果が実現できることを実証したのは素晴らしい。

消費電力の内訳。ちなみに0.6pJ/bitは0.7V動作で16GT/秒以上の場合。12GT/秒以下では0.5pJ/bit、0.5V動作ならそれぞれ0.25pJ/bit、0.3pJ/bitと定義されており、次はこうしたケースの実証に移るのかもしれない

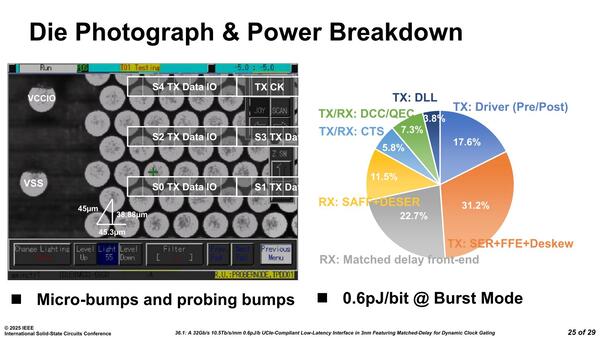

下の画像が今回のまとめである。ちなみに消費電力はClock Gatingを使うと0.46pJ/bitとなり、これは12GT/秒以下の場合の0.5pJ/bitを満足する値である。少なくともTSMCの3nmを利用したダイを利用することで、UCIe 1.1に定義されたAdvanced Packageの仕様を満たすことが可能、という実例を示せたのはかなり大きな成果であろう。

UCIeのI/F IPを提供開始したという発表は複数社(Alphawave Semi/Avery/Cadence/Synopsys)が行なっているのだが、Standard PackageはともかくAdvanced Packageに関しては消費電力が厳しいだけに、どこまで実現できるか疑わしいところもあったのだが、実際に動作させた結果が示されたわけで、実現困難/不可能な数値ではないことが立証できたのは喜ばしいことではある。

ただ逆説的に言えば、UCIeを利用してChipletを構築しようとすると、TSMC N3以降が必要になる、ということかもしれない。Computeチップレットはそれでもいいのだろうが、IOチップレットなどはTSMCのN5やN6を使うケースが多い。こうしたものでも今回と同等のことが可能なのか、それとももっとスピードを落とさないとだめなのか、はまだ議論の余地がありそうだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ