ロードマップでわかる!当世プロセッサー事情 第779回

Lunar LakeではEコアの「Skymont」でもAI処理を実行するようになった インテル CPUロードマップ

2024年07月08日 12時00分更新

前回はLunar LakeのPコアであるLion Coveを解説したので、今週はEコアのSkymontを解説しよう。

TremontとGracemontの違いはキャッシュ容量だけ

Skymontの前身であるCrestmontではそれなりに強化された

Pコア同様、Eコアの方もAlder LakeからRaptor Lakeまではあまり変わっていない。もっと正確に言えば、Alder LakeのGracemontの元になったのはLakefield/Elkhart Lakeで採用されたTremontコアである。これがAlder Lake/Raptor LakeではGracemontになったが、違いは1次命令キャッシュが32KB→64KBに増量されただけである。

このGracemontはSierra Forestでも採用されたが、2次キャッシュの容量が4MB決め打ちになった以外に外から見える違いはない。Meteor Lakeで採用されたCrestmontは、Tremontからそれなりに強化された。

Core Ultra特集の第3回で下のスライドが示されているが、こちらではIPC向上以外に分岐予測の強化とVNNIを始めとするAI関連命令、それとThread Directorの対応強化などが挙げられている。

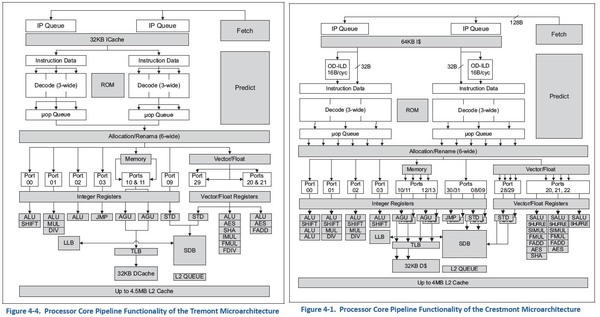

IPC向上であるがインテルのIntel 64 and IA-32 Architectures Optimization Reference Manual Volume 1の最新版(Version 50)からTremontとCrestmontのブロック図を抜き出してまとめたのが下の画像である。

フロントエンド、つまりPrefetch~Allocation/Renameまではほとんど差がない(1次命令キャッシュと、新たに追加されたOD-ILD(On-Demand Instruction Length Decoder)が目立つ程度でしかない。

ところが発行ポートの方はだいぶ増えており、ALUが7→12、FPU/Vectorが3→5に増えている。これにともない実行ユニットもALUが同時4つ、AGUも4つ、さらにJMP/STDも2つづつになっているし、FPU/Vectorの方もLoad/Store以外に3命令の同時実行が可能になるなど、かなり強化されているのがわかる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ