今回は、フランスのVSORAが提供するTyrプロセッサーを取り上げたい。創業は2015年とやや古め。創業者はJulien Schmitt氏とTrung Dung Nguyen氏の2人だが、2人ともフランスのDiBcomという、TV向けのデジタルチップセットを製造するファブレスメーカーに勤務していた。

DiBcomは2011年にParrotというドローンメーカーに買収され、両氏ともそのままParrotに移籍している。最終的なポジションはSchmitt氏がDSP&ASIC group manager、Nguyen氏がSenior Signal Processing Engineerだったようだ。

もともとDiBcomは、高性能・低消費電力なDSPを核としており、これを利用して欧州で利用されているさまざまなデジタルTVの標準規格に向けたチップセットを提供していた。一方のParrotはドローンの製造にあたり、やはり高性能かつ低消費電力なプロセッサー技術を必要としており、なのでDiBcomの保有していた製品ポートフォリオというよりも核となるDSP技術を買収した、というのが正しいところだろう。

Schmitt氏とNguyen氏は2015年にParrotを辞してVSORAを設立する。ちなみにCEOには、DiBcomの創業者兼CTOであり、ParrotでもDigital Tuner部門のCTOだったKhaled Maalej氏が就いているが、なぜかMaalej氏はVSORAの創業者ではないらしい。

5G NRで通信可能な信号処理プロセッサー

そんなVSORAであるが、当初目指していたのはAIではなく信号処理の方向だった。創業から3年後の2018年9月、VSORAはLETI(フランス電子情報技術研究所)と共同で、3GPP Release 15の物理層をマルチコアDSPで実装したことを発表している。

この時VSORAはMPU-801というSingle Core DSP Processorと、これを4つ統合したMPU-3201というMulti Core DSP Processorの2つをラインナップしている。

VSORAは当時はまだ製品売りというよりもIP売りの会社であり、LETIとの共同発表もLETIのニーズに合わせてMPU-3201をカスタマイズしたものを提供し、これを実装(どうも発表を読んでいるとシリコンを製造したというよりはFPGAに実装したようだ)上で5G NRの物理層のアルゴリズムを搭載、これを利用した5G NRの通信実験に成功したようだ。

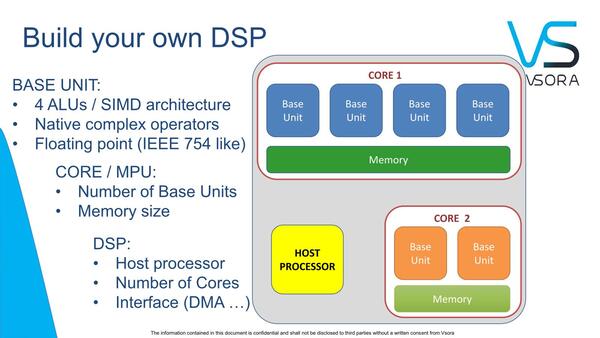

ちなみにこのMPU-801/3201の内部構造はさっぱり不明なままである。説明によれば以下の特徴を持っているそうだ。

- High processing-power eliminates the need for specific coprocessors and ensures greater flexibility

(高い処理性能により、特定のアクセラレーター類を必要とせず、高い柔軟性を確保する)

- Customizable DSP-processing power

(DSPの処理能力をカスタマイズ可能)

- Customizable Floating-point Arithmetic Logical Units

(FPUもカスタマイズ可能)

- Efficient low power instructions

(効率の高い低消費電力な命令セット)

- High level description of algorithms

(アルゴリズムを高レベル言語で記述可能)

- Mixing signal processing and embedded software

(信号処理を演算命令に混在可能)

- One code for data-link layer & physical layer

(データリンク層と物理層を1つのコードで記述可能)

- Separates automatically codes running on the DSP and on the CPU

(DSP上で動作するコードとCPU上で動作するコートを自動的に分離)

それをどうやって実現したのか? の説明は一切ない。もう少し詳細な説明が下の画像だが、これでも中身がさっぱりわからない。カスタマイズの自由度が高いことはわかるのだが、それだけである。とは言え、5G NRの基地局の処理ができる程度の性能がある(これもその基地局の規模次第なので、性能を一概に議論するのは難しいのだが)ことしかわからない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ