東芝は2月9日、組込み機器向けの超低消費電力アナログAIアクセラレーターチップを開発したと発表した。

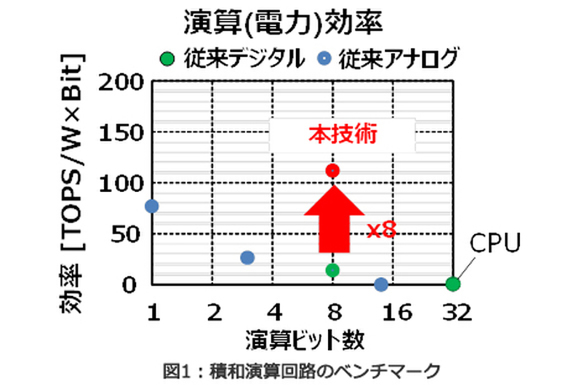

ニューラルネットワーク処理の大部分を占める積和演算処理を行なうアナログ回路。独自の発振回路を採用し、発振時間と発振周波数を動的に制御することで演算処理を行なっている。従来のデジタル回路で処理されていた乗算・加算・記憶をひとつの回路で可能となり、デジタル回路と比べて1/8という大幅な電力削減が可能という。

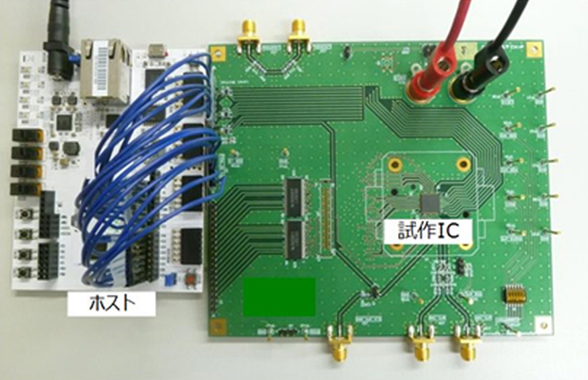

開発したAIアクセラレーターチップを用いて画像認識や故障検知のニューラルネットワークの推論処理のデモ動作にも成功。今後実用化に向けて開発を進めるとしている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります