Knights Coveで時間を稼ぎ

その次のKnights Runが本命

ではどうするのか? というのが次の話。今のところインテルはKnights Hillに代えてKnights Coveという次の製品を2019~2020年の段階でまず投入、次いでKnights Runという製品を2022年までに投入し、これがAurora用になると言われている。

まずマイクロアーキテクチャーだが、Knights Hillは基本的にKnights Landingのプロセス微細化版と目されていた。Knights Landingは14nmプロセスを利用し、Silvermont(つまりAtom系列)の整数パイプラインにAVX512エンジン×2を組み合わせたコアを最大72個搭載する。

AVX512エンジンはDP(64bit)の値を8つ同時に扱え、しかもFMAD(Fused Multiply and Add:積和演算)処理が可能なので、1サイクルあたり16FLOPS相当になる。ハイエンドの「Xeon Phi 7290F」の場合、72コアで1.5GHz駆動なので、16(FLOPS/サイクル)×72(コア)×1.5GHz=3456GFLOPSという計算である。

これがKnights Coveでは、コアがIceLake-SP(Skylake-SPの10nmプロセス版)に32GBのHBM2を搭載したものになると、もっぱらの噂である。コア数は38ないし44だそうで、こちらもSkylake-SPに1つのコアにAVX512エンジンを2つ搭載したものになる。仮に動作周波数が3GHzと仮定すると以下の性能になる。

- 38コア:16(FLOPS/サイクル)×38(コア)×3GHz=3648GFLOPS

- 44コア:16(FLOPS/サイクル)×44(コア)×3GHz=4224GFLOPS

というあたりで、Knights Landingから微増というあたりでしかないが、おそらくこれはポイントリリーフで、次のKnights Runではもっと多数(~88コア程度?)のコアを集積したものになるとみられる。そうでないと1EFLOPSが実現できないからだ。

仮にAuroraの規模を維持する(5万ノード)と仮定すると、1ノードあたり20TFLOPSほどが実現できないとまずい。1ノードにXeon Phiを2つ、Xeon SPを1つという構成だとすると、Xeon Phiが88コア/3GHz動作、Xeonが38コア/3GHz動作ならだいたいノードあたり20.5TFLOPSほどが出せる計算になる。

時期的にはKnights Runや、これと対になるXeon SP(こちらはコード名がIce Ageだそうだ)は7nmプロセスを使ったものになるだろうが、あとはこの7nmがどこまで消費電力を抑えられるかということに尽きそうだ。

ところで、なぜKnights CoreでいきなりXeonコアを使うかだが、Knights Landingのチーフアーキテクトを勤めたAvinash Sodani氏が2016年9月にCavium Inc.に転職しており、Xeon Phiのチーム自身も現在弱体化していると噂されている。

すでに命令セットはAVX512でXeonとXeon Phiは共通化されており、Xeon-SPコアをHPC向けにローカルキャッシュを強化(このためにHBM2を利用)する程度でお茶を濁さざるを得ないということだろう。このあたりもなかなかインテルの苦しい事情が透けて見える。

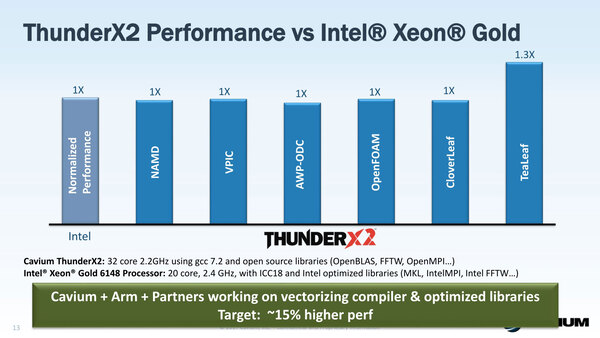

ちなみに今年のSC17では、そのCaviumは下記のプレゼンテーションを出しており、インテルとやる気満々である。もっともそのCaviumもMarvell Semiconductorに買収されるというニュースが今月に入って流れているので、この先どうなるのか不明ではある。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ