TDNN(Time Domain Neural Network)回路

東芝は11月7日、低消費電力でディープラーニングを実現する人間の脳のような半導体回路を開発したと発表した。

現在のディープラーニングは大量の演算を高速で処理することから、高速なプロセッサーを必要とし、多量の電力を消費する傾向がある。また、一般的なノイマン型コンピューターでは、メモリーからデータを頻繁に取り出して演算、保存を行なうため、データ移動のための電力も大きいことが課題となっている。

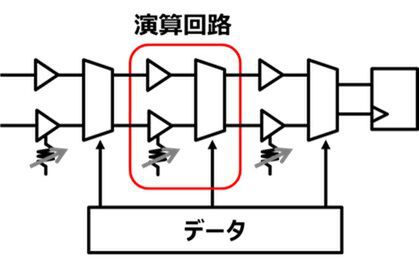

東芝では2013年に「時間領域アナログ信号処理」と呼ばれる技術を開発。これは信号がゲートを通り抜ける遅延時間をアナログ信号として用いるもので、デジタルのON/OFFや、電圧値によるアナログ回路とは異なり、低消費電力かつ信号線1本というシンプルなしくみでアナログ回路を構成できるというもの。

時間領域アナログ信号処理のイメージ

この時間領域アナログ信号処理技術を演算回路として用いるディープラーニング用演算回路TDNN(Time Domain Neural Network)を開発。ディープラーニングの演算1つを3つの論理ゲートと1bitのメモリーで実現でき、チップサイズを大幅に小型化しつつ、完全な並列化も可能とした。東芝ではSRAMを利用したチップを試作、ディープラーニングの基本動作である画像認識を行なった結果、演算にかかるエネルギーはこれまでの記録よりもはるかに少ない1/6以下になったという。

東芝では、さらに電力消費の少ない抵抗変化型メモリ(ReRAM)を使用するTDNNの開発を計画しており、ニューラルネット・チップの小型低消費電力化を進めるという。

本記事はアフィリエイトプログラムによる収益を得ている場合があります