Control Processorは完成したが

Address/Data Processorが完成せず

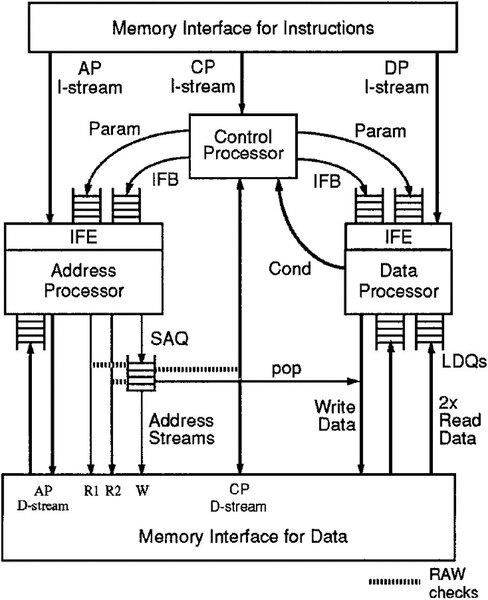

そのACRI-1であるが、内部構成は下の画像のとおりである。Address ProcessorとData Processorの両方を制御するControl Processorを追加することで、効率的に稼動させる狙いである。

画像の出典は“Decoupled Architectures for Complexity-Effective General Purpose Processors”。

これはControlもDecoupleの対象になるということで、DCAR(Decoupled Control/Access/Execute)と呼ばれている。

Address ProcessorとData ProcessorはそれぞれIFE(Instruction Fetch Engine)とIFB(Instruction Fetch Block)を搭載しており、Control Processorが各々に対する命令制御を行なう形だ。

文献を読む限りは、命令のフェッチそのものはメモリーから直接IFEが取り込む形で、Control ProcessorはそのIFEに対して「次の命令を取り込むか」といった制御のみをIFB経由で行なっていたようだ。

ちなみに条件分岐などは未サポートで、有効な命令のみを実行する(つまり投機実行はサポートしない)というのは、時代を考えれば無難なところか。

さて、ACRI-1のプロセッサーであるが、まずControl ProcessorにはDECのAlpha AXP 21064が採用されることになった。これはもともとJacques Stern氏がBullの時代にCRAYやDECと関係を深めていたという事情がからんでいるらしい。

DECのAlpha AXP 21064については連載291回で説明したので詳細は割愛するが、当時としてはわりと高速な部類に属した。幸いなことにDECからはCPUだけでなくOSも利用できた。

DECがAlpha向けに提供したDEC OSF/1に、Address Processor/Data Processorをサポートするようなカスタマイズを加えたバージョンがACRI-1用に用意されたが、これもStern氏とDECの結びつきがあっての話だったのだろう。

問題はAddress ProcessorとData Processorである。当初、ACRIはこれをECL(エミッタ結合論理)もしくはGaAs(ガリウム砒素)で製造したMIPSベースのコアで実装することを考えていたが、そもそもAlpha AXP 21064が64bitプロセッサーなので、Address Processor/Data ProcessorはMIPS 64をベースに開発しようと考えていたようだ。

ただ当時のMIPSはまだSGI傘下にあり、ECLベースのMIPS64コアといえばR10000~R16000(R18000はキャンセル)系列ということになるが、これをカスタム可能な形で出すことは拒否した。SGIのハイパフォーマンス系列システムに使われる予定だったコアをカスタマイズしたいと言われても素直に了承できないのは当然である。

MIPSは32bit系列コアの提供を申し入れたらしいが、これはACRI側が拒否したようだ。結局ACRIは独自のコアを開発することになった。Address Processorはアドレス演算のみを行なうVILW風の命令セットを持つ構成、Data Processorはひたすら数値演算のみを行なう構成だったそうで、それならWeitekのFPUでも良かったのではないかとすら思える。

Address ProcessorとData ProcessorはMotorolaのECLプロセスを使って製造され、SNI(Siemens Nixdorf Informationssysteme:現在はFujitsu Siemens ComputersとWincor Nixdorfに分離してしまった)のパッケージを利用するはずだった。はずだった、というのはこのパッケージの提供をSNIが1995年に中止してしまったからだ。

一方、メモリーコントローラーやその他の周辺回路はTIのBiCMOS ICを使って構築され、これとプロセッサーをつなぐインターコネクト(8×8のクロスバースイッチ)はVitesse Semiconductor(現在はMicrosemi Corporationの子会社)のGaAsベースの高速スイッチで構築された。された、というか「されるはずだった」というところか。

このように開発に紆余曲折があってなかなか進まなかったものの、1994年の春に開催されたCeBITではマシンのモックアップを展示するなど、一応前進してはいた。

画像の出典は“The Dead Supercomputer SocietyのACRI”。

ただこのACRI-1は唐突な終わり方をする。150名が開発作業を行なうわけだから、経費はどんどん増えていく。1989年にはフランスおよびヨーロッパから公債を得ており、さらにプライベートファンドから資金を集めていた同社。1993~1994年にかけては、合計で8400万スイスフランを得ていた。

1993年の換算レートで言えば63億円ほどの金額になるが、これでは開発に全然足りなかった。1993年の終わりに監査が入り、1994年に結果が出されるが、その結果は「この先の活動を続けてゆくためにはさらに1億スイスフランの追加資金が必要」というものだった。

もちろん、そんな金額を急に用意できるわけもなく、1995年2月23日に破産してしまった。ACRIには、Control ProcessorのAlpha AXP 21064のみを実装したACRI-1の作りかけがあるだけで、Address ProcessorやData Processorが完成するのを待っている状態だったらしい。

なにが悪かったかといえば、いきなり100人超のエンジニアを雇ったというのは経費の点で無茶が多かった。基本的な実装方針が決定するまでの間、彼らは事実上遊んでいたようなものだったからだ。

インターネットアーカイブに、当時のエンジニアの何割かのリストが記されているが、明らかにプロセッサーの開発当初には不要な役職の方も何人か見られる。スタートアップの基本である「最初は小さく」を守らなかったがゆえの必然的な帰結かもしれない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ