1キャビネット以内の構成では性能を発揮

Cellを構成するプロセッサーそのものは40bitのアドレス空間を持つ(KSR-2では64bitになった)。さすがに1088個ものCellがアドレス空間を共用すると、連続的にアドレスをマッピングしたとしてもCellの識別だけで11bit必要だ。

一方、ローカルキャッシュの32MBには25bit必要なので、最低でも36bitアドレスが必要になる。この時点で汎用のプロセッサーでは足りない(ほとんどが32bitアドレス)ことになる。なので、チップそのものはKSR製の独自のものである。

内部は4つのブロックに分かれており、以下で構成される。

| CEU(Cell Execution Unit) | 命令の解釈や一部の実行を行なう。 |

|---|---|

| XIU(I/O Processor) | 名前の通りI/O処理を行なう。 |

| IPU(Integer Processing Unit) | 整数演算を行なう。 |

| FPU(Floating Point Unit) | 浮動小数点演算を行なう。 |

ちなみに英国のeBayにこのKSR-1のチップだけが出品されているのだが、チップそのものは6種類(3-1333-01~3-1138-01)ある。

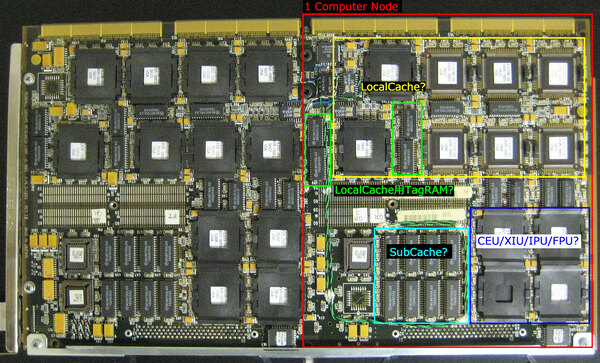

KSR-1のボード写真を見ると1コンピュートノードあたりこれらのチップを合計で12個利用している。内訳は下記のとおり。

| チップ名 | 個数 |

|---|---|

| 3-1333 | 1個 |

| 3-1334 | 1個 |

| 3-1335 | 1個 |

| 3-1336 | 1個 |

| 3-1337 | 4個 |

| 3-1338 | 4個 |

おそらく基板で右下にある3-1333~3-1336がCEU/XIU/IPU/FPUで、その左脇にあるSRAM×8がサブキャッシュ(合計512KB)、上段の8つのチップは32MBのローカルカッシュで、その周りにあるものがローカルキャッシュ用のTag RAMではないかと思うのだが、確証はない。

命令セットは2命令同時実行のVILWであり、CEU/XIU向けの命令×1とIPU/FPU向けの命令×1を同時に実行できる。FPUは1サイクルあたり最大2つの計算が可能(乗加算命令を同時に実行可能だった模様)となっている。

なお、動作周波数そのものは20MHzで、このためCellあたりの最大性能は40MFLOPSという計算になる。ちなみにKSR-1はシャープの1.2μm CMOSプロセスで製造された。

超並列でしかもALLCACHEアーキテクチャーという尖った構成だけに、プログラミングはさぞ難しかろうという気もするのだが、少なくともKSRはこの点に関してかなり努力はした。

C/C++に加え、Micro Focus COBOL(Micro Focusは1976年以来ずっとCOBOLを提供し続けてきているベンダーで、現在も存在する)、Oracle PRDBMS、ADBのMATISSE OODBMS(オブジェクト指向データベース)などが提供されており、またOSとしてはUNIXベース(OSF/1の派生型:Machカーネルベースという説明もあった)が提供された。

さて、最初の製品は1991年9月にオークリッジ国立研究所に納入された。当初は32cellの構成(つまりRing 0が1個だけ)で、翌1992年にはこれが64cellの構成になった。

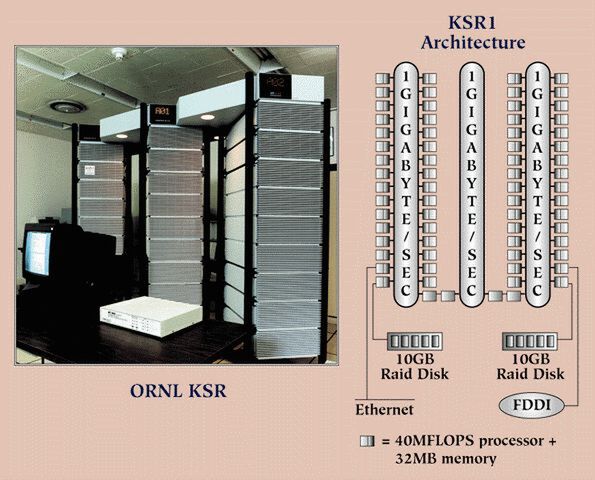

下の画像がその構造だが、Photo02のボードを2枚(つまり4cell)収めたキャビネット×8が1つのラックに収められているようだ。

キャビネットは9個あるが、上の画像にもあるようにRAID DISKやFDDI/EthernetなどのI/F部を収めるのに別のキャビネットが必要だったと思われる。

それぞれのラック内のキャビネットに収められたCellは1GB/秒のRing 0で接続され、キャビネット間は上の画像でラック上端間をつなぐ白い構造内に収められたRing 1でつながっていると思われる。

オークリッジ国立研究所からは、この初期(32cell)構成での評価レポート(Kendall Square Multiprocessor Early Experiences and Performance)が1994年に公表されている。

これによればCRAY用に記述された高温超伝導物質のエネルギー密度のシミュレーション用プログラム(Fortranで17000行)の移植はそれほど難しくなく、32cell構成で243MFLOPSの性能を実現できたとしている。

またデータベースについても、KSR製のQuery DecomposerというソフトウェアとOracleを組み合わせることで、16cellまでの構成で効率93%(14.88倍速)が実現できたという論文もある。

ただその一方で、先のRamachandran氏の論文では取り扱うデータ構造が大きくなると、32MBのローカルキャッシュは容量が小さすぎ、またRing 0を超えてRing 1経由でのアクセスになったとたんにネットワークがボトルネックになって性能が上がらないとしている。

とりあえず1キャビネット以内の構成ではそれなりの性能が出るが、それを超える場合にはやや工夫が必要、という評価だった。

→次のページヘ続く (粉飾決済が発覚して倒産)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ