IDF 2010の目玉のひとつは、次世代マイクロアーキテクチャーの「Sandy Bridge」だ。今回は細かいセッションの情報から、Sandy Bridgeの概要をお届けする。

Sandy Bridgeの4大特徴とは?

Sandy Bridgeの特徴を簡単にまとめると以下のようになる。

- グラフィックスプロセッサー(以下GPU)をCPUダイに統合し、CPUコアとGPUでキャッシュを共有させて、より効率的な実行を可能にしたこと。

- 256bit幅のSIMD演算命令である「AVX」を装備していること。

- ビデオエンコードなどのアクセラレーターを装備して、特定の処理に関して高速化していること。

- ターボ・ブーストが強化され、より高いクロックでの実行が可能なこと。

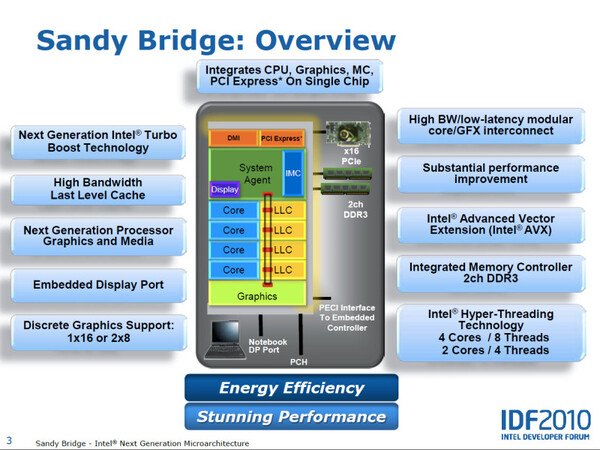

図1はSandy Bridgeのブロック図だ。Sandy Bridgeの内部は大きく4つに分けられる。CPUコア、LLC(Last Level Cache)、GPU、そしてSystem Agentだ。System Agentは従来のチップセットが持っていた機能に対応するもので、この中にメモリーコントローラー(IMC、Internal Memory Controller)がある。

System AgentとLLC、GPUはリングバスで接続されており、CPUコアやGPUはキャッシュを通して、このリングバスでSystem Agentと接続してメモリーアクセスを行なう。LLCは各コアごとに作られているが、リングバスで接続されているため、インテルはこれを共有キャッシュだとしている。

リングバスによる接続部分はSandy Bridgeの中心ともなる機構で、この構成から「橋」(Bridge)という名称につながったのだと言われている。

改良されたCPUコア

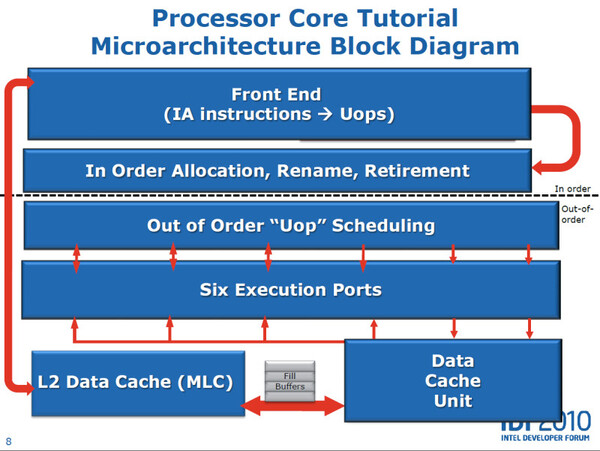

まずはCPUコアから見ていこう。図2がCPUコア全体のおおまかなブロック図だ。CPUコアは、インオーダーの部分とアウトオブオーダーの部分に大きく分かれる。インオーダー部分には、キャッシュから命令を取得してμOPSに変換するフロントエンド部と、μOPSをアウトオブオーダー部に送り込み、実行終了を確認する部分からなる。

アウトオブオーダー部は、インオーダー部から来たμOPSを依存関係などを見ながら実行していくスケジューリング部と、実際の計算を行なう実行ポート、データキャッシュなどからなる。

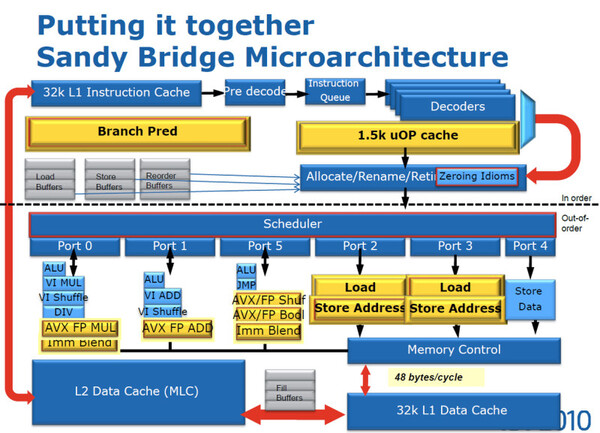

命令のフェッチからデコードまでは、これまでのCore 2やNehalemアーキテクチャーに対して強化されている。まず、一旦変換したμOPSをキャッシュしておく「μOPキャッシュ」(1500μOPSを格納)があり、ループなどの場合には、再度x86命令をデコードすることなく実行される。このあたりの制御は、ここにある「Branch Predictor」(分岐予測器)が制御する。

またSandy Bridgeでは、μOPキャッシュがヒットし続けている間、1次キャッシュからデコーダーまでの電源を落として、消費電力を下げられる。デコーダー部分は新命令(AVX命令)もあるため、大きく変化していると思われるが、プレデコード、キュー、デコーダーという並びは変わっていない。

こうしてμOPSとなった命令は、「Allocation/Rename/Retirement」部分に入る。ここでは、以下のアウトオーダー部分へ命令を発行していく。なおSandy Bridgeでは、レジスターリネーミングの機構に「Retirement Register File」ではなく「Physical Register File」(物理レジスターファイル)を採用しているため、データのコピーはひとつだけで、処理後にデータを移動させる必要がない。

AVXが256bit幅の演算に対応しているため、浮動小数点関連の演算ユニットは、これまでの倍幅の256bit幅になっている。これにより、浮動小数点の乗算などを高速に処理することが可能になっている。

また、データのロード・ストアも強化されており、クロック1サイクルあたり最大2つの読み出しと、ひとつの書き込み(各最大16byte)を可能にしている。キャッシュメモリーは32KB×8Wayの1次データキャッシュ、256KBの2次データキャッシュ(MLC、Mid Level Cache)をコア内に持つ。

図3は詳細なブロック図で、黄色い部分がSandy Bridgeで改良された部分になる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります