リングバスでSystem Argent、キャッシュ

グラフィックスを接続

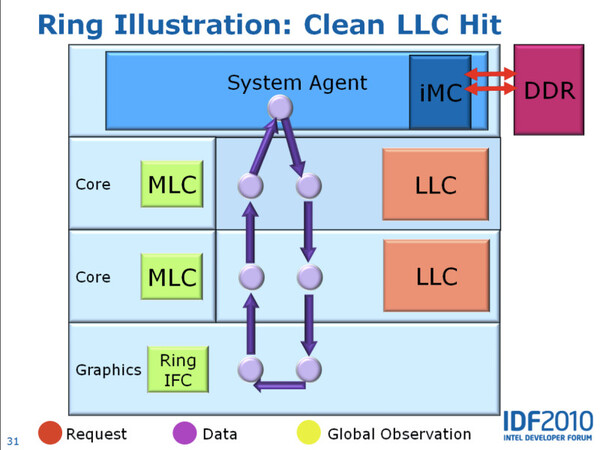

Sandy Bridgeの特徴のひとつが、内部のリングバスだ。キャッシュおよびGPU、System Agentを高速なリングバスで接続し、キャッシュはCPUコア、GPU、System Agentで共有している(図4)。System Agentは従来のチップセット部分に相当し、ここにメモリーコントローラーや画面表示用の回路、PCI Expressインターフェースなどがある。

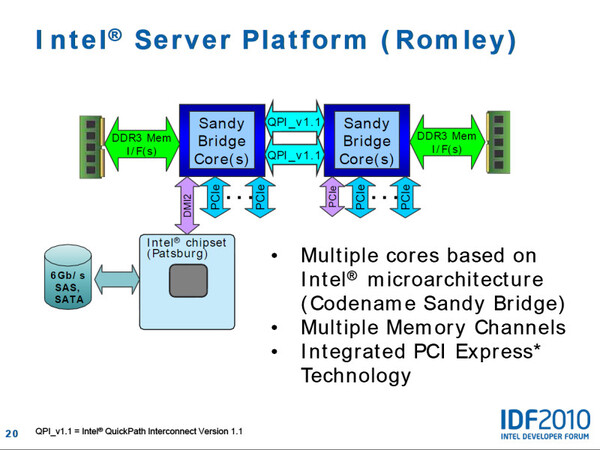

またこの構造は、CPUコア数の変化に柔軟に対応可能だという。当初はデュアルコアおよびクアッドコアが用意され、サーバー用の複数ソケットに対応したプロセッサーでは、QPIでプロセッサー間を接続する(図5)。

このリングバスは、Data(32byte)、Request、Acknowledge、Snoopの4つの内部リングバスで構成されている。3GHzで動作するリングでは、各ノード間を最大96GB/秒で接続できる。リングバスでの接続となるため、CPUコアやGPUの追加や削除は、容易に行なえる。ある種のモジュラー構造といえる。また、CPUコアはリングバスの転送方向を選べるため、最短経路での接続が可能だ。

CPUコアやGPUは、リングバスに対してメモリーデータのリクエストを送る。キャッシュにデータがある場合、キャッシュはリクエストへの応答を返し、データを送出する。リクエストは、リングバスを使ってキャッシュを巡回するため、CPUコアが直接接続していないキャッシュにあるデータも取得できる。各CPUコアのキャッシュは、他のキャッシュに何が入っているのかを、あらかじめ知る必要もない。そのため、コアごとにキャッシュが分かれていても「共有キャッシュ」として動作できるわけだ。

どのキャッシュも該当のデータを持っていない場合には、リクエストはSystem Agentに到達し、ここでメモリーコントローラーから読み込まれる。

Sandy Bridgeのグラフィックス機構

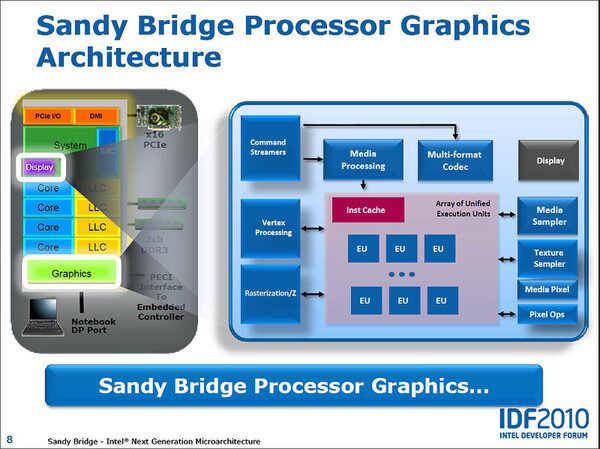

Sandy Bridgeの特徴のひとつであるGPUは、CPUコアと同一ダイ内に集積されている。先述したようにリングバスでLLCを共有しつつ、CPUコアと同様にメインメモリーをアクセスする。いわゆるフレームバッファ(ビデオメモリー)は、メインメモリー上に取られる。また、メディアアクセラレーション機能としてビデオデコーダが搭載されている(図6)。

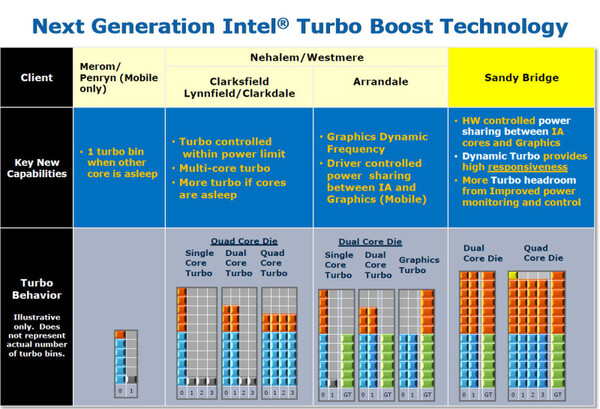

CPUコアと同じダイに集積されているため、GPUの電力管理もCPUコア同様に細かくできる。またSandy Bridgeでは、ターボ・ブースト時にGPU部分の余裕を利用することも可能だ(図7)。

GPUは特定の機能を実行する部分とプログラマブルな部分に分かれている。プログラマブル部分は、内部に演算を実行するEU(Execution Unit)を複数持つ。固定機能部分には、マルチフォーマット対応のコーデックやメディアプロセッサーなどがある。なお、GPUとしてはDirectX 10相当だという。

「Multi-format Codec」は、MPEG-2やVC1、AVCなどに対応し、この部分のみでエンコード/デコードができる。エンコーダー/デコーダーは高速に並列処理を行ない、稼働時間を短くして不要なときには休むという形で、低消費電力化されている。逆に言えば、フルで動作した場合には実時間以下でのエンコード/デコードが可能な性能を持つ。

ビデオエンコード/デコードなどは、あらかじめ用意されている固定機能部分で実行できるが、EUを使ってプログラマブルに処理することも可能で、これから登場する新しいフォーマットにも容易に対応が可能だという。