既報のとおり、「Sandy Bridge」のコード名で紹介されてきた新しいCore i7/i5/i3シリーズのプロセッサーが発表された。製品のバリエーション紹介やベンチマークによる性能解説はそれぞれの記事を参照していただくとして、本稿ではSandy Bridgeの内部アーキテクチャーについて解説する。

なお、本稿では特に区別する必要がない限り、新プロセッサーをまとめてSandy Bridgeと記述する。

Sandy Bridgeアーキテクチャーの概要

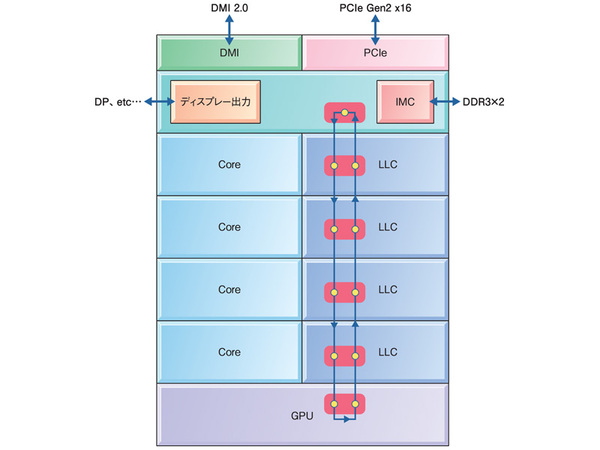

図1はSandy Bridge全体の構造である。これは4コアのCore i7/5のケースで、CPUコアが2つのCore i3もラインナップされている(モバイル向けは2コアのCore i7/i5もあり)。主な特徴としては、以下の要素がNehalem(Core i7-900番台)/Clarkdale(デスクトップ向けのデュアルコアCore i5/3)世代から大きく異なる点である。

- ClarkdaleまでのCore iシリーズと異なり、CPUコアとGPU、従来のMCHの働きをする「System Agent」が、すべてひとつのダイに集約されている。

- 「LLC」(Last Level Cache、Nehalem世代までの3次キャッシュに相当)が複数に分割され、全CPUコア+GPUで共用される。

- 各CPUコア/LLCとGPU、System Agentは、双方向のリングバスで接続される。

そのほかに細かい特徴としては以下のものが挙げられる。

- ディスプレーコントローラーをGPUコアから分離してSystem Agent側に実装したことで、画面のリフレッシュがリングバスの帯域を占有する可能性を排除した。

- GPUコアの性能を改善した。

- DMIを2倍の転送速度を持つDMI 2.0に改善した。

- CPUコア自体のIPCを改善した。

- AVX命令を実装した。

次ページからは、各特徴をもう少し細かく見ていこう。

この連載の記事

-

第13回

PCパーツ

マザーないけど…… Sandy Bridgeの「Core i3」がデビュー! -

第12回

PCパーツ

不具合によりP67/H67搭載マザーが全ショップで販売停止中 -

第11回

マザーボード

インテル、Intel 6チップセットのエラーを公表 -

第10回

PCパーツ

Sandy Bridge発売日にインテルがイベントを開催 -

第9回

マザーボード

「Sandy Bridge」対応マザーボード一斉発売!【その他編】 -

第8回

マザーボード

「Sandy Bridge」対応マザーボード一斉発売!【Intel編】 -

第7回

マザーボード

「Sandy Bridge」対応マザーボード一斉発売!【Gigabyte編】 -

第6回

デジタル

「Sandy Bridge」対応マザーボード一斉発売!【ASRock編】 -

第5回

マザーボード

「Sandy Bridge」対応マザーボード一斉発売!【ASUSTeK編】 -

第4回

PCパーツ

自作ユーザー集結! インテル新CPUが深夜に販売解禁! -

第3回

自作PC

ついに登場! 新型Core i7/i5シリーズの価格をチェック - この連載の一覧へ