DDR5の高い性能がハッキリわかった! 貴重なXPGとADATAのDDR5メモリーをテスト

提供: エイデータテクノロジージャパン

DDR5 SDRAMが話題になっている。長く主流として君臨していたDDR4 SDRAMの後継で、新たに第12世代Coreプロセッサーのメインメモリーとしてサポートされたことで、その性能や機能に注目が集まっているわけだ。

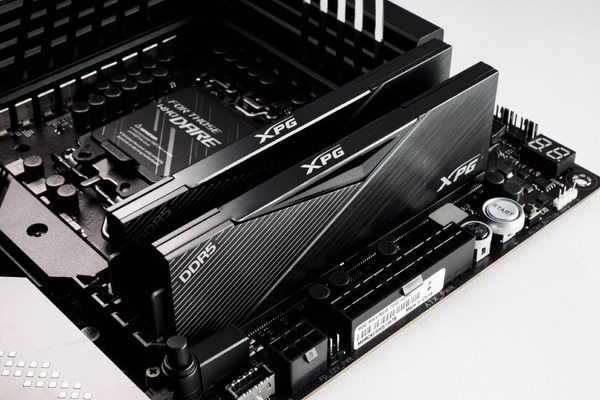

メモリー関連製品で実績のあるADATAからもゲーミングブランドの「XPG」、オリジナルの「ADATA」の両方のブランドからDDR5メモリーの製品が登場している。今回は仕様や新機能を解説しつつ、これらを利用して挙動や性能のチェックをしていきたい。

DDR5 SDRAMの特長とは DDR4とは何が違う?

DDR5 SDRAMは、DDR4 SDRAMの後継となる高速メモリー規格だ。DDRの由来は「Double Data Rate」。クロックに同期し、1クロックにつき2回データ転送をすることから来ている。その根本的なしくみはDDR5でも変わっていないが、高速化を実現するためにさまざまな改良がされている。

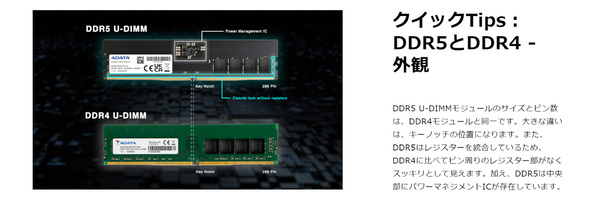

DDR5 DIMMのピン数は288ピン。DDR4と同じだが、電気的な互換性はない。端子部の切り欠きの位置も異なり、DDR5 DIMMをDDR4 DIMMソケットに差したり、その逆にDDR4 DIMMをDDR5 DIMMソケットに差すことはできない

さて、DDR5の重要なポイントを箇条書きにすると以下のようになる。

・DDR4の後継となる高速メモリー規格

・DDR4とは物理的にも電気的にも互換性がない

・データレートはJEDEC標準仕様で6400MT/s

・データの転送効率が改善され、実効帯域が向上

・電力管理を行なう「PMIC」の実装

・I3Cインターフェイスの採用

・Intel XMP 3.0の機能強化

上記に挙げた以外にもDDR5の新機能として取り上げられるものに「オンダイECC」がある。DRAMチップ内部における転送速度高速化に伴う信頼性を確保するため、ダイ内部の転送段階でエラー訂正機能を持たせている。信頼性を高める機能には違いないのだが、大幅な高速化にともなう課題解決の1つとして追加されたものであり、取り立ててどうという機能ではない。サーバー向けで見られるモジュールレベルのECC機能とはまた別の機能だ。

また、従来64bitのチャネルを32bitの独立したチャンネルとして扱えるようになっているが、これも一部で誤解がある。マルチコア環境でのアクセス効率化など実効帯域の向上に貢献する仕様の1つではあるが、従来の意味でのデュアルチャネルアクセス(64bit×2=128bitアクセス)が1モジュールでできるようになったわけではない。

DDR5とDDR4の主な違い

| DDR5 | DDR4 | |

|---|---|---|

| データレート | 3200~6400MT/s | 1600~3200MT/s |

| 1チップあたりの最大容量 | 64Gbit | 16Gbit |

| オンダイECC | 実装 | ― |

| 動作電圧 | 1.1V | 1.2V |

| PMIC | 実装 | ― |

| 最大バースト長 | 16 | 8 |

| プリフェッチ | 16n | 8n |

| 最大バンクグループ | 8 | 4 |

| サイドバンドIF | I3C(12.5MHz) | I2C(1MHz) |

データレートが大幅向上、実効帯域もアップ

DDR5の最大の特徴は、大幅に高速化されたデータレートだ。JEDEC仕様書上のデータレートは、DDR4では3200MT/sが最高であったのに対し、DDR5では6400MT/sと2倍に高速化されている。

DDR4ではJEDECで定められている標準仕様を超えるデータレートの高速メモリが登場しているが、それはDDR5も同様。すでに8400MT/s、12600MT/sのデータレートをもつ高速モジュールも予告されている。

データの転送効率も大きく改善されている。たとえば、仮にデータレートが同じ3200MT/sであっても、実測のデータ帯域はDDR5のほうがDDR4よりも大幅に速い。

この効率改善に特に関連するのが、バースト長。貨物列車の貨物車両の数のようなものだと思ってもらえばよいだろう。つまり、一度のコマンドのやりとりで転送できるデータ量が2倍になっている。(DDRでない)SDRAMの時代からずっと8だったのが、16に拡張されたというのはインパクトのある変更だ。

このほか、プリフェッチ(先読み)とバンクグループの倍増、バンクリフレッシュ方式の変更、64bitのチャネルを2つの32bitサブチャネルとしてアクセスできる仕組みを導入するなど、高速転送、および転送効率を改善するための仕様がさまざま導入されている。

バンクグループはDDR4から導入された仕組み。異なるバンクグループに連続してアクセスすることでアクティベーションやリフレッシュのロスを隠蔽し、データ転送速度を高めるしくみだ。DDR5ではグループ数を2倍に拡大している

新たにPMICを実装、サイドバンド通信も高速化

DDR5の動作電圧は1.1VとDDR4より少しだけ低い。この電圧は、DDR5ではモジュール上のPMIC(PowerManagement IC)と呼ばれる電圧レギュレータチップで生成するようになっている。電圧を安定させるためのチップコンデンサの実装を最小限に抑えつつ、安定して高速に電流を供給できるほか、電力効率の向上も見込める。ただし、高速動作で相殺されるため、実際の製品がモジュールレベルでDDR4よりも省電力かと言うと、必ずしもそういうことではないだろう。

DDR5では、新たにPMICを実装しており、DRAMの駆動電流はここで生成される。電圧を安定させるためのチップコンデンサの実装を最小限に抑えつつ、安定して高速に電流を供給でき、電力効率の向上も見込める

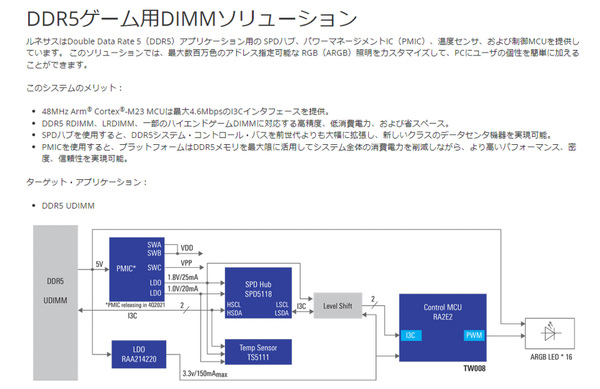

サイドバンドの通信インターフェイスがI2C(1MHz)からI3C(12.5MHz)に変更され、高速化されている点は将来的に影響があると思われる。このインターフェースはアドレッサブルRGBのコントローラや温度センサーなどの接続に使われる。つまり、この手の機能をより多機能にできる余地があるということで、将来的にはメモリーやマザーボードの付加価値を高める要素に活用されていくことが考えられる。

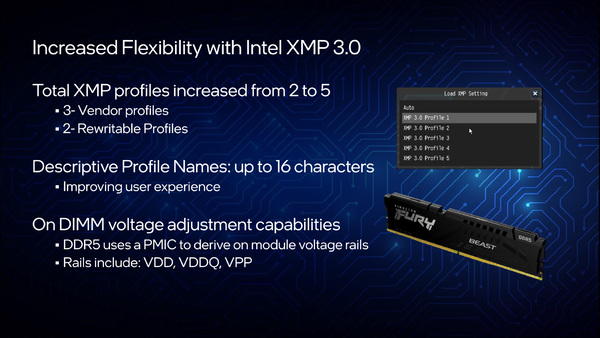

高速メモリーの半自動設定をするためのIntel XMPもDDR5用に拡張され、バージョンが3.0となった。従来2つだったベンダープロファイルは最大3つ格納できるようになり、新たにユーザープロファイルも格納できるようになっている。PMICが実装されたことでより柔軟に電圧のコントロールができるようになっており、それもプロファイルで指定できるため、OC効果はより期待できる。

この記事の編集者は以下の記事もオススメしています

-

デジタル

ADATA/XPGが新製品発表会 日本未発売の本格15型ゲーミングノートや電源、DDR5メモリーなど -

デジタル

ミリタリー系マザーボードにベストマッチ! 「ラギッドスタイル」の新メモリー「XPG SPECTRIX D45G」をテスト -

デジタル

今売れ筋のDDR4-3200対応メモリー 最近のメモリー事情を整理しつつ、お手頃価格のXPG製品をテスト -

デジタル

XPGからRGB LEDを備えるDDR5-6000対応メモリーが発売 -

sponsored

かなり入手しやすくなってきたDDR5メモリー XPGの高速タイプ「DDR5-6400」の威力をテスト! -

PCパーツ

【特価情報】安すぎるDDR5メモリー! 16GB×2枚組が1万4980円の大特価