(株)日立製作所は10日、動作クロック周波数が750MHzで、容量が144Mbitの“キャッシュDRAM LSI”を開発したと発表した。これは高速アクセスが可能だが集積度を上げるのが難しいSRAMの代わりに、ゲート長0.18μmのDRAM混載プロセスを採用し、大容量DRAMとCMOS論理回路を同一チップ上に混載することで動作周波数を上げ、容量を増やしたもの。同社では次世代の高性能サーバー用に開発したという。

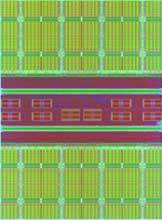

| 動作クロック周波数750MHz、容量144Mbitの“キャッシュDRAM LSI” |

|---|

“キャッシュDRAM LSI”は、DRAM部のランダムアクセスタイムが8.0ns、シーケンシャルアクセスタイムが5.3ns、内部のピーク転送速度が毎秒48GBとハイエンドプロセッサーに対応できるのが特徴。LSIの不良をチェックするための新開発のテストエンジン(高速テストパターン発生回路/判定回路)を内蔵し、自己テストが行なえるため、高速大容量メモリーのテスト効率が向上したという。テストパターンの発生回路には、2種類のマイクロプログラム(テストシーケンスを記述するための“マイクロコード”、テストパターンのタイミングを制御する“ナノコード”)による制御方式を採用したとしている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります