インテル株式会社

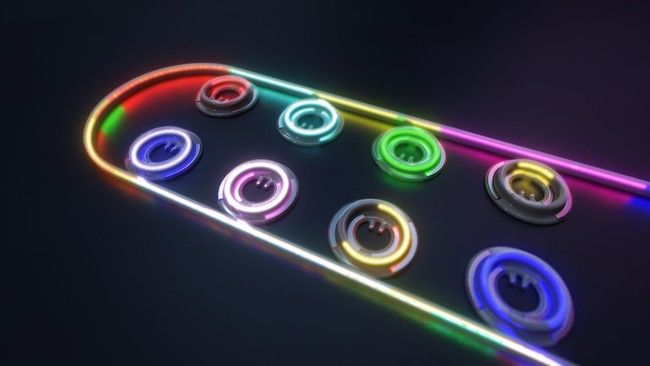

均一な出力電力と波長間隔により厳密にコントロールされた8波長レーザーアレイをシリコンウエハー上に実装するデモを公開

*2022年6月28日に米国で発表された資料の抄訳です。

最新情報: インテルラボは、データセンター内のコンピューティング・シリコンとネットワーク全体をつなぐ通信帯域幅の拡大に向けた次のフロンティアである「フォトニクス集積」の研究における、大幅な前進を発表しました。この最新の研究の特徴としては、1つのシリコンウエハー上に完全に統合され、業界の仕様を上回る+/-0.25デシベル(dB)の極めて高い出力電力の均一性と±6.5%の均一な波長間隔を実現する、8波長分散帰還(DFB)レーザーアレイのデモを含めた、業界最先端を進む多波長集積光モジュールにおける進歩が挙げられます。

「この新たな研究は、均一な間隔かつ高密度で波長を配置することで、出力電力の均一性を十分に維持することが可能であると証明しています。最も重視すべきは、インテルの工場で行っている既存の製造とプロセス管理でこれを実現できること、つまり次世代のコパッケージド・オプティックスと光コンピューティング・インターコネクトの量産を大規模に進めていく明確な道筋が確保されている点です」とインテルラボ シニア・プリンシパル・エンジニア ハイシェン・ロン(Haisheng Rong)は述べています。

発表の意義:この進歩によって、人工知能(AI)やマシンラーニング(ML)などネットワーク負荷の高い新たなワークロード向けのコパッケージド・オプティックスや光コンピューティング・インターコネクトを含め、フォトニクスの光源を将来的な量産アプリケーションに必要なパフォーマンスで製造できるようになります。このレーザーアレイは、インテルの300mmシリコン・フォトニクス製造プロセスで設計されました。これは量産と広範囲への導入を促進する技術です。

ガートナーは、2025年までに広帯域幅データセンター全体で通信チャネルの20%以上をシリコン・フォトニクスが占めるようになり(2020年の5%未満から拡大)、将来的な市場規模は26億ドルになると予測しています。低消費電力、広帯域幅、データ転送の高速化に対する需要の高まりが、データセンターをはじめ幅広いアプリケーションに対応可能なシリコン・フォトニクスを求めるニーズの拡大を加速しています。

重要な理由:1980年代に、銅線から置き換わり、光接続が用いられるようになりました。これは、金属ケーブル経由で伝送される電気インパルスにはない、光ファイバーに備わる広帯域という光伝送の特性によるものです。その後、部品のサイズとコストを抑えられることから、このテクノロジーの効率性はさらに向上し、スイッチ機器からデータセンター、ハイパフォーマンス・コンピューティング(HPC)環境まで、ネットワーク・ソリューションでの光インターコネクトの利用はここ数年で大幅に広がっています。

電気インターコネクトの性能面での限界が指摘される中、シリコン回路と光パスを同一のパッケージ内に並べて実装することで、電力効率が向上し伝送距離が拡大した将来的なI/Oインターフェイスになると期待されています。こうしたフォトニクス・テクノロジーは、インテルの工場施設内で既存のプロセス技術により開発されました。大規模な製造に有利なコスト削減にもつながります。

高密度波長分割多重化(DWDM)テクノロジーを使用する最新のコパッケージド・オプティックス・ソリューションは、帯域幅の拡大に加え、フォトニクス・チップの物理的なサイズを大幅に縮小できると見込まれています。しかし、これまで均一の波長間隔と出力電力でDWDM光源を製造することは、簡単ではありませんでした。

今回の進歩によって、均一の出力電力を維持しながら、一定の波長間隔で光源を分離することが可能になり、光コンピューティング・インターコネクトとDWDM通信に求められる要件の1つを満たす結果となっています。光インターコネクトを備えたこの次世代のコンピューティングI/Oは、AIやマシンラーニングの広帯域幅ワークロードで求められる高度な要件に合わせ、カスタムメイドが可能です。

実現する仕組み:8波長DFBアレイは、インテルの商用300mmハイブリッド・シリコン・フォトニクス・プラットフォームで設計および製造されました。このプラットフォームは、光トランシーバーの量産製造に使われてきたものです。このイノベーションは、厳密なプロセス制御下で300mmシリコンウエハーを製造するのと同じリソグラフィー技術を採用することで、相補型金属酸化膜半導体(CMOS)の大規模製造工場内で量産レーザーの製造容量を大幅に引き上げる、画期的な進歩と言えます。

インテルはこの研究で、まずシリコン内の導波路回折格子の定義に高度なリソグラフィー技術を、次にIII-V族ウエハー・ボンディング接続プロセスを使用しました。この手法が、3~4インチのIII-V族ウエハー工場で製造される従来の半導体レーザーと比較して、波長の均一性を高める結果へとつながっています。さらに、レーザーを高密度に集積することで、周辺温度が変化した場合でも、アレイがチャネル間隔を維持することが可能になっています。

次のステップ:インテルはシリコン・フォトニクス技術の先駆者として、ネットワーク・インフラストラクチャーの効率化と柔軟な処理能力に対する高まるニーズに応えるソリューションの開発に努めています。現在開発中のコア技術となるビルディング・ブロックには、光の生成、増幅、検出、変調、CMOSインターフェイス回路、パッケージ統合テクノロジーなどが含まれます。

また、8波長集積レーザーアレイ技術が持つ多くの側面は、将来的に提供される光コンピューティング・インターコネクト・チップレット製品の一部として、インテルのシリコン・フォトニクス製品部門が構築しています。まもなく発売となる製品は、CPU、GPU、メモリーなどのコンピューティング・リソース間を1秒当たり数テラビットの速度で接続する、電力効率の高い高性能なインターコネクトです。この高集積レーザーアレイは、量産製造と大規模導入を支え、コンパクトでコスト効率の高いソリューションを実現する重要な要素となっています。

詳細情報:フォトニクス集積

https://www.intel.com/content/www/us/en/research/integrated-photonics.html?wapkw=integrated%20photonics¥

本記事はアフィリエイトプログラムによる収益を得ている場合があります