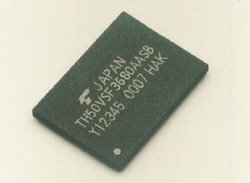

(株)東芝は9日、『TH50VSF3680AASB』と『TC50VSF3681AASB』を発表した。これらは、0.22μmプロセスの8MbitSRAMと、0.2μmプロセスの64Mbit

NOR型フラッシュメモリーを搭載する、業界初というスタック型マルチチップパッケージ(MCP)。携帯電話など小型携帯端末に搭載することを想定し、縦9×横12mmという小型BGA*パッケージを採用している。『TH50VSF3680AASB』ブートブロックはトップアドレス、『TC50VSF3681AASB』はボトムアドレス。3月末にサンプル出荷が開始され、サンプル価格は1万円。4月より数万個、第3四半期より30万個以上のレベルで量産出荷の予定。

|

|---|

| 『TH50VSF3680AASB』 |

*Ball Grid

Array:PGA(Pin Grid Array)のピン部分をボール状の半田にしたもの

そのほか同社は、以下の製品の商品化を発表した。

・TSOP(Thin Small Out-line Package)タイプのパッケージを採用した8Mbit SRAM(単体)。3月末より販売し、サンプル価格は4000円。4月より数万個、第3四半期より50万個以上のレベルで量産出荷の予定。

・4Mbitまたは8Mbit SRAMと32Mbit NOR型フラッシュメモリーを組み合わせたスタック型MCP。4月より販売する予定

本記事はアフィリエイトプログラムによる収益を得ている場合があります