積み重ねとエッチングを繰り返して

誕生するトランジスタ

シリコンウェハーの製造は、実は日本が強く、最大手が信越化学の半導体事業部、2番手がSUMCOで、両社合わせて50%を超える世界シェアがある。ここでは非常に精度の高い単結晶インゴットをまず製造、次にこれを薄く切り出してシリコンウェハーを製造する。

場合によってはウェハーに表面加工を行なったり、SOI(Silicon On Insulator)向けに複数のウェハーを張り合わせる事例もあるが、ここまでがウェハーベンダーの作業となる。半導体製造ベンダーはこのウェハーを買い付けるところから始まる。

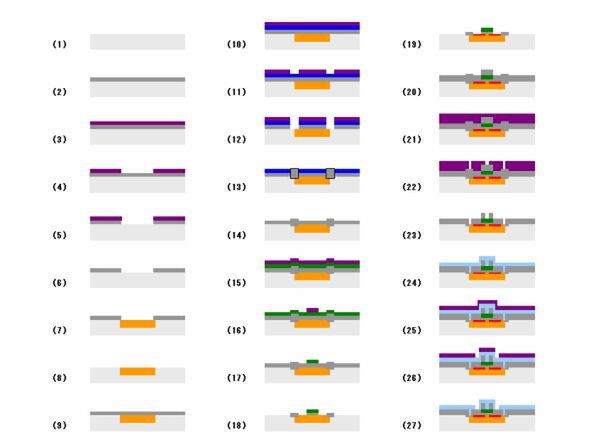

では、その買ってきたウェハーにどうやってトランジスタを形成するか、であるが簡単にまとめただけでも27もの手順になった(図5)。

ちなみにこれでもかなり省いて書いてるのだが、順に説明すると以下の通りになる。

- (1) ウェハーを洗浄・感想・研磨して準備を整える。

- (2) 二酸化シリコン(SiO2)の膜を表面に形成する。これはベーキング(高温の炉の中に入れる)を行なうことで、酸素と反応して表面に二酸化シリコンの膜が形成される。

- (3) SiO2膜の上に、フォトレジスト膜を塗布する。

- (4) フォトレジストを行ない、不要な部分のパターンを除去する。ちなみに(3)と(4)の手順がいわゆるリソグラフィと呼ばれるもので、実際にはある種の光に反応する感光塗料を塗布した後、マスクを被せてその上から光を当て、その後で像(銀塩写真と同じ理屈)を行なうと、マスクを被せた部分が残るという仕組みである。

- (5) パターンがなくなった部分をエッチングにより溶かす。ちなみにエッチングは、初期は液体を使って除去していたが、最近はドライエッチングと呼ばれる液体を使わない方法を使う。

- (6) 残っているパターンを科学的に除去する。

- (7) ウェハ全体にイオン(P型ウェハーの場合はここでP(リン)イオン)注入を行う。注入というものの、Pをイオン化し電界で加速してウェハーに打ち込む、いわば電子銃のような方法である。この際、SiO2膜がない部分にはSiウェハー中にこのイオンが進入し、その部分が半導体になる。

- (8) 二酸化シリコン膜を一旦除去する。

- (9) あらためて二酸化シリコン膜を形成する。

- (10) 二酸化シリコン膜の上に、シリコン窒化膜(Si3N4)を形成する。

- (11) シリコン窒化膜の上に、フォトレジスト膜を形成する。

- (12) フォトレジスト膜の上にパターンを転写し、エッチングする。このエッチングは先の(5)に近い。

- (13) フォトレジスト膜を除去し、そこに二酸化シリコンを厚く積層する。

- (14) シリコン窒化膜を除去する。さらに(13)で積層した二酸化シリコンと元々の二酸化シリコン膜を成長させて一体化する。

- (15) 表面に多結晶シリコン膜(PolySi)を形成し、その上にフォトレジスト膜を塗布する。

- (16) パターンを転写する。ここでトランジスタのゲート電極が形成される。

- (17) エッチングにより、ゲート電極以外の多結晶シリコン膜を除去する。

- (18) 次に多結晶シリコン膜を利用して改めてエッチングを行ない、二酸化シリコン膜を除去する。

- (19) ここで再びイオン注入する。ホウ素(B)イオンを打ち込むとPMOSに、砒素(As)イオンを打ち込むとNMOSになる。

- (20) トランジスタが形成されたので、改めてウェハー全体に厚く二酸化シリコン膜を形成する。

- (21) 全体にフォトレジスト膜を塗布する。

- (22) トランジスタの電極部のみを削るようにパターンを転写する。

- (23) エッチングを行ない、マスキングを除去することで二酸化シリコン膜に電極が形成される。

- (24) 全体にアルミニウムを塗布する。

- (25) 全体にフォトレジスト膜を塗布する。

- (26) 電極同士がショートしないようにパターンを転写する。

- (27) エッチングを行ない、マスキングを除去することで、アルミニウムの電極が形成される。

ちなみにかなり省いた、というのは各々の処理の前に必ず洗浄や乾燥という手順が入るからだ。さらにエッチングと一言で済ませているが、実際は用途に応じて数段階の手順を取ることが多い。一昔前(2000年以前)の頃で、このトランジスタを形成するのに200以上の段階が必要になっていた。

この連載の記事

-

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 - この連載の一覧へ