基礎知識の説明が延々と続いて、そろそろ飽きてきたと思うので、今回から実際のプロセスの段階を解説していこう。

インテルのプロセスを振り返る

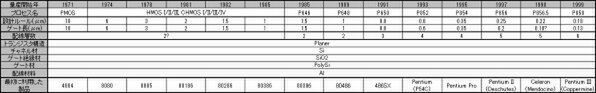

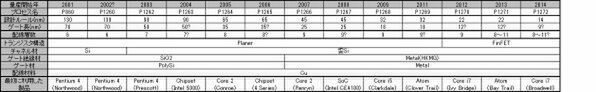

下表は、インテルのロジック向けプロセスを順に並べていったものである。1999年以前と2000年以降で2段に分かれているのは、表が長すぎて入りきらないという問題もあるのだが、もう1つ意味がある。1999年以前は「Free lunchの時代」、2000年以降は「Free lunchが終わった時代」である。それについては次回以降に説明していく。

| インテルのロジック向けプロセス年表(1971~1999) | ||||||||

|---|---|---|---|---|---|---|---|---|

| 量産開始年 | 1971 | 1974 | 1978 | 1981 | 1982 | 1985 | ||

| プロセス名 | PMOS | HMOS I/II/III, CHMOS I/II/III/IV | ||||||

| 設計ルール(μm) | 10 | 6 | 3 | 2 | 1.5 | 1 | ||

| ゲート長(μm) | 10 | 6 | 3 | 2 | 1.5 | 1 | ||

| 配線層数 | 2? | |||||||

| トランジスタ 構造 |

Planer | |||||||

| チャネル材 | Si | |||||||

| ゲート絶縁材 | SiO2 | |||||||

| ゲート材 | PolySi | |||||||

| 配線材料 | Al | |||||||

| 最初に利用 した製品 |

4004 | 8080 | 8085 | 80186 | 80286 | 80386 | ||

| 量産開始年 | 1985 | 1989 | 1991 | 1993 | 1995 | 1997 | 1998 | 1999 |

| プロセス名 | P646 | P648 | P650 | P852 | P854 | P856 | P856.5 | P858 |

| 設計ルール(μm) | 1.5 | 1 | 0.8 | 0.6 | 0.35 | 0.25 | 0.22 | 0.18 |

| ゲート長(μm) | 1.5 | 1 | 0.8 | 0.6 | 0.35 | 0.2 | 0.18? | 0.13 |

| 配線層数 | 2 | 2 | 3 | 4 | 4 | 5 | 5 | 6 |

| トランジスタ 構造 |

Planer | |||||||

| チャネル材 | Si | |||||||

| ゲート絶縁材 | SiO2 | |||||||

| ゲート材 | PolySi | |||||||

| 配線材料 | Al | |||||||

| 最初に利用 した製品 |

80386 | 80486 | 486SX | Pentium (P54C) |

Pentium Pro | Pentium II (Deschutes) |

Celeron (Mendocino) |

Pentium III (Coppermine) |

| インテルのロジック向けプロセス年表(2000~2014) | |||||||

|---|---|---|---|---|---|---|---|

| 量産開始年 | 2001 | 2002? | 2003 | 2004 | 2005 | 2006 | |

| プロセス名 | P860 | P1260 | P1262 | P1263 | P1264 | P1265 | |

| 設計ルール(nm) | 130 | 130 | 90 | 90 | 65 | 65 | |

| ゲート長(nm) | 70 | 70 | 50 | 50? | 35 | 35? | |

| 配線層数 | 6 | 6 | 7 | 7? | 8 | 8? | |

| トランジスタ 構造 |

Planer | ||||||

| チャネル材 | Si | 歪Si | |||||

| ゲート絶縁材 | SiO2 | ||||||

| ゲート材 | PolySi | ||||||

| 配線材料 | Cu | ||||||

| 最初に利用 した製品 |

Pentium 4 (Northwood) |

Pentium 4 (Northwood) |

Pentium 4 (Prescott) |

Chipset (Intel 5000) |

Core 2 (Conroe) |

Chipset (4 Series) |

|

| 量産開始年 | 2007 | 2008 | 2009 | 2011 | 2012 | 2013 | 2014 |

| プロセス名 | P1266 | P1267 | P1268 | P1269 | P1270 | P1271 | P1272 |

| 設計ルール(nm) | 45 | 45 | 32 | 32 | 22 | 22 | 14 |

| ゲート長(nm) | 25 | 25 | 18 | 18 | 12? | 12? | 9? |

| 配線層数 | 9 | 9? | 9 | 9? | 9 | 8~11 | 8~11? |

| トランジスタ 構造 |

Planer | FinFET | |||||

| チャネル材 | 歪Si | ||||||

| ゲート絶縁材 | Metal(HKMG) | ||||||

| ゲート材 | Metal | ||||||

| 配線材料 | Cu | ||||||

| 最初に利用 した製品 |

Core 2 (Penryn) |

SoC (Intel CE4100) |

Core i5 (Clarkdale) |

Atom (Clover Trail) |

Core i7 (Ivy Bridge) |

Atom (Bay Trail) |

Core i7 (Broadwell) |

さて話を1999年以前の表に絞ろう。ロジックプロセスとして最初に利用されたのは1971年の「i4004」であるが、これはまだCMOSになる前の、ただのPMOSのみで実装されており、回路中で一番短いピッチの寸法が10μmであった。

実際のところ、CMOSが広く利用されるようになるのは大分後、具体的には8086の派生型でCHMOSを採用した製品の発表があった1978年あたりから、次第に利用され始めたはずだ。ただ筆者の記憶が正しければ、1978年のCMOS版8086は発表こそあったものの、あまり出回らなかった。現実問題としては1979年以降にまともに量産に入れたのではないかと思う。

ではなぜCMOSが普及しなかったのか。それは連載236回ではあえて説明しなかったCMOSの欠点があったからだ。簡単におさらいしておけば、CMOSではNMOSとPMOSという2種類の半導体を組みあわせて組み合わせ回路を実現する。ということは以下の問題がある。

- トランジスタの数が2倍必要になる

- PMOSとNMOSの特性が揃ってないと動作が滅茶苦茶になる

まずトランジスタ数だが、NMOSやPMOSではインバーターが1個で実現できるが、CMOSでは2つ必要になる。ということは、1970年代のようにトランジスタ数の縛りが厳しい(なにしろ一定面積に入れられるトランジスタ数が恐ろしく少ない)環境では、相当に贅沢な構成ということになる。

もう2つが特性の話。連載236回でCMOSにおけるインバーターの動作を説明したが、ここで2つのトランジスタのスイッチング速度が激しく違うと、正しく動作しないのは明らかである。

連載236回でも解説した、NMOSとPMOSを組み合わせたインバーターの回路図

したがってNMOSとPMOS、2種類の異なるトランジスタの特性をきちんと揃えないといけないわけだが、これは当時の技術ではかなり難しかった。これがディスクリート、つまりトランジスタを単体で取り出した部品であれば、トランジスタの特性を1個1個測定したうえで、うまくマッチする組み合わせを見つけてCMOS回路を構成するという悠長な真似も不可能ではない※1。

※1:CMOSとは関係ないが、特に真空管オーディオの世界では出力マッチングが重要とされており、複数の真空管を手に入れてエージングしながらうまくマッチするものを選び出してペアにするというのが、一部でごく普通に行なわれているようだ。

しかし、ICではそんな無茶な真似はできないので、ある程度高い精度でNMOS/PMOSのトランジスタ特性を近いところに合わせる必要があり、これが難しかったということだ。したがって、最初のプロセスはPMOSのみだったのも無理ないことである。

ちなみにこの10μmのPMOSプロセスは、後継である「4040」や、8bit化した「8008」でも利用されている。ただ「8008」の場合は同じ10μmと言いながら、若干の変更を施したEnhanced-mode PMOSを利用している。この当時はまだCPUの設計とプロセスの設計が一緒くただった時代でもあり、具体的にどうプロセスが変わったかなどは論じるだけ無駄である。

※お詫びと訂正:記事初出時、表内の表記に一部が誤りがございました。訂正してお詫びいたします。(2014年2月11日)

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ