90nm世代のプロセス「P1262」を採用したPrescott。非常に難産だった

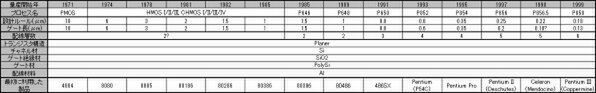

各社のロードマップ アップデートを挟んだため1ヵ月ほど間が空いてしまったが、再びプロセッサーのプロセスについて解説していく。今回は2003年にインテルが導入した90nm世代の「P1262」の話である。

銅汚染問題の次は

リーク電流対策

配線を銅に切り替えたことで高速化の障害が1つ減ったものの、相変わらずトランジスタの高速化は難しく、よりゲート長を短縮する必要があったのだが、これにあわせてもう1つ懸念事項が出てきていることは業界でも広く知られていた。それがリーク電流だ。

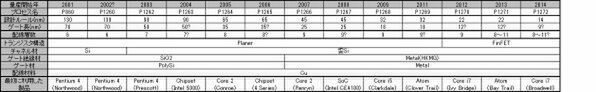

上のグラフは東京大学の桜井貴康教授が2003年10月に示したものだが、トランジスタが動作する際には、リーク電流と呼ばれるものが一定量発生する。蛇口をきっちり閉めても、ほんのわずかながら水が漏れるようなものだ。

大きな水栓ならあまり問題にならないが、水栓というかパッキングが小さくなると、どうしてもわずかに漏れることは避けられない。同様にトランジスタも、小型化によってあちこちから電流が漏れ出てくる。このリーク電流には3種類ある。

- 意図せずにドレインからソースに漏れてしまう、サブスレッショルド・リーク電流(Subthreshold Leakage)

- ゲートから漏れてしまうゲート・リーク電流(Gate Leakage)

- Drain/Sourceの電極から直接漏れてしまう、ジャンクション・リーク電流(Junktion Leakage)

グラフからもわかる通り、これまでリークといえばサブスレッショルド・リーク電流が主であった。このグラフ、縦軸が対数になっていることが肝である。

例えば2005年に予定されているトランジスタであれば、ゲート・リーク電流はサブスレッショルド・リーク電流の10分の1でしかないが、2008年頃にはこれが同等になり、2011年には10倍になると予測しているわけだ。実際には、ゲート・リーク電流はこの予測より早期に問題になってきている。

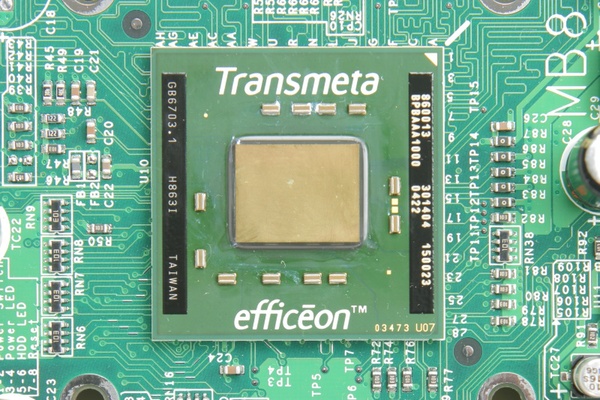

Transmetaはこの対策として一種のBody Biasを利用した「LongRun 2」という技術を開発し、NECやSONY、富士通/東芝/NVIDIAなどにライセンスを供給するものの、結局自社のプロセッサー「Efficeon」はLongRun 2を実装しないまま会社が終了してしまった。

最近ではSuVOLTAというメーカーが、やはりこのBody Biasを利用した「DDC(Deeply Depleted Channel)」なる技術を開発、いくつかのベンダーにこれをライセンス供与している。

話を戻すと、このゲート・リーク電流はトランジスタの性能との相反関係にある。なぜゲートから電流が漏れるのか。それはゲートの厚みが薄いためだ。したがってゲート・リーク電流を減らすにはゲートの厚みを増せばいい。

ところがゲートを厚くすると、スイッチングの速度が遅くなる。トランジスタを高速化するためには、ゲートは薄い方が有利なのである。2003年頃は、どのくらいの厚みでバランスを取るか、各社頭を悩ませていた時期でもある。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ