前回までは、ある程度量産実装に近いところまで来ている近未来の技術を中心に解説したが、今週来週はもう少し遠い未来の、「可能性はある」レベルのものをいくつか取り上げたい。

III-V族トランジスタ

トランジスタの構造そのものに新素材を使用する

III-V族トランジスタ

III-V族トランジスタというのは、周期表で言うところのIII族(13族)とV族(15族)を組み合わせてトランジスタを作る方法である。

「なんじゃそれは」という方のために、Wikipediaを引用させていただくと、これが周期表である。列方向に1~18までの番号がついているのがわかるかと思うが、ここで13の番号がついたB/Al/Ga/In/Ti/...といった元素がIII族、15の番号がついたN/P/As/Sb/Bi/...といった元素がV族と示される。

ちなみにIII族のUnr(ウヌントリウム:原子番号113)とかV族のUnp(ウンウンペンチウム:原子番号115)は、理論的にはあるとされつつまだ未発見である。またIII族のEs(アインスタニウム)やV族のNd(メンデレビウム)はアクチノイド(放射線元素)なので、半導体に使うのはあまりに不向きということで、これは普通入らない。

このIII-V族の化合物(2種類以上の元素を組み合わせたもの)を利用したトランジスタを、俗にIII-V族トランジスタと呼ぶ。

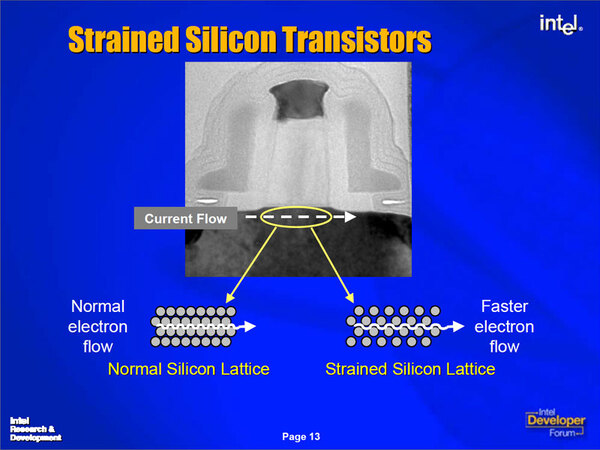

実は、こうした材料そのものはこれまでも色々試されてきた。連載247回でHKMGの話を解説したが、この際にはTi(チタン)を初めとする様々な材料を試したことがIEEEへの発表で明らかになっているし、歪シリコンでは(III-V族ではないが)Ge(ゲルマニウム)を利用していることを解説している。

こうした、Si以外の材料をこれまでも広く利用はしてきたが、それはあくまでトランジスタの周囲(絶縁膜やベース素材)に限られていたが、そうではなくトランジスタの構造そのものにもIII-V族材料を使おう、という発想だ。

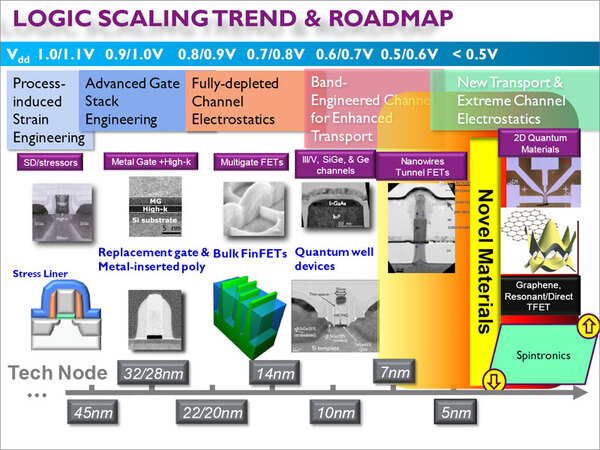

下の画像はIMECのAaron Thean博士が2012年6月に行なった“BEYOND SILICON CMOS”というプレゼンテーションからの抜粋である。

博士は、ノードで言えば10nm以下、動作電圧で言えば0.6~0.7V付近まで来ると、もうCMOSでは無理であり、III-V族もしくはSiGe(シリコンゲルマニウム)やGeのトランジスタがそろそろ要求される、と考えている。またトランジスタの構造も、従来のプレーナやマルチゲート(つまりFinFETなど)ではそろそろ限界で、量子井戸構造が必要と説明している。

右上の画像がその新素材を組み合わせたレイアウト例で、NMOSはIII-V族化合物で、PMOSはSiGeで構成することを考えているとする。この量子井戸の話は次にするとして、とにかくこうした新材料を使うことが、10nm未満では絶対に必要、というのが業界全体のコンセンサスとして認識されつつある。

これは別にIMECだけでなく、ITRSのロードマップでも明確に述べられている。2013年のITSのロードマップの中のIRC Overview(PDF)では“High mobility channel materials such as Ge and III-V have been considered as an enhancement or replacement for Si channel for CMOS logic applications.”(高い電子移動度を持つ、GeあるいはIII-V族材料は、CMOS Logicアプリケーション向けのSiチャネルの代替/改良の材料として考慮されるべきである)という一文がある。

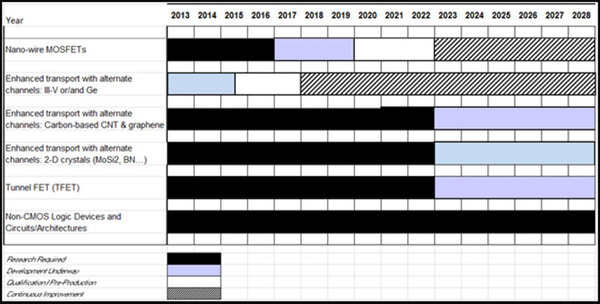

また、PIDS(Process Integration, Devices, and Structures)にはこんなロードマップも示されている。

Nano-wireは2016年、CNT(Carbon Nano Tube)やトランジスタ構造の変更、Tunnel FETは2022年までそれぞれ基礎研究が続いて、そこから量産に向けた開発が始まるとしている。

非CMOSのLogic Deviceにいたっては2028年まで延々と基礎研究を続ける(2028年で終わるという意味ではなく、2028年までは間違いなく基礎研究が続くの意味)という段階。

それに対し、III-V族あるいはGeはすでに基礎研究は終わっており、今は量産に向けた開発に入っているとみなされている。2015年中旬からはその技術の品質確認とか量産試作が始まり、2018年には実用化されるとしている。

ITRSのロードマップがあてにならない(口の悪い業界関係者は「あれはインテルの願望だ」とまで言い切る)のはともかく、現状のIII-V族は他の将来技術に比べると、遥かに現実的なポジションに居ると考えてよい。

もっともこうしたSi以外の材料も、「すべてにおいてSiを代替できる」ものは今のところ存在しない。ある特性はSiを大幅に上回っている半面、別の特性はSiと比べ物にならないほど悪いといった話は日常茶飯事である。

では、そうした材料を複数組み合わせれば上手く欠点がカバーできるかと言うと、今度は「組み合わせたら材料同士がケンカしてしまって使い物にならない」具合だ。あるいはPMOSは作れるけどNMOSは作れない(もしくはその逆)というケースも多い。

それでも、とにかく候補となる材料は多く、かつ組み合わせ方に無限に近い可能性があるあたり、時間をかければ最適な候補が見つかる、と考えている人は多いようだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ