Cortex-A8でスーパースカラーの実装に踏み切る

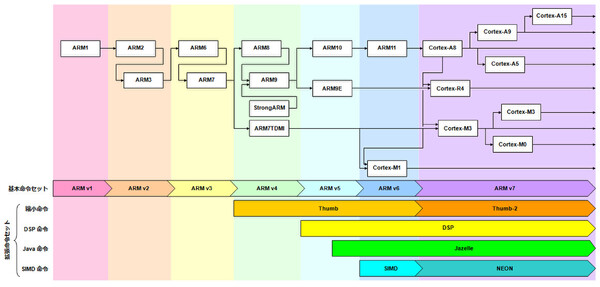

性能向上と並行して、ARMは次世代コアの開発も行なっており、これは「ARM v7」アーキテクチャーとして2005年に発表された。ARM v7に関してはアーキテクチャーそのものと同時に、実装したコアである「Cortex-A8」も同時に発表されている。Cortex-A8の名前は、スマートフォンやタブレット端末のCPUとして、よく目にするだろう。

Cortex-A8の設計目標は「1GHz駆動で2000DMIPS」、つまり2.0DMIPS/MHzの実現である(図6)。これの実現のために、ARMとしては初のスーパースカラーの実装に踏み切った。

図7はCortex-A8のパイプライン構造であるが、図左にあるように命令フェッチの時点で2命令/サイクルの取り込みを行ない(矢印が2本出ている)、これをデコードして同時2命令発行を実現している。

実行ユニットは3つ用意され、それぞれは独立して実行されるという仕組みだ。図7では4つに見えるが、「ALU pipe 0」と「MUL pipe 0」は実はひとつのパイプで、ALUかMultiply(乗算)のどちらかを実行できる。ただしアウトオブオーダーは、Coetex-A8ではまだ実装されていない。

当然ながら、これを支えるメモリーシステムも大きく変化している。ロード/ストアパイプラインや、これと連動するバスインターフェースユニットのパイプラインは、2次キャッシュの存在を前提に構成されていることがわかる(図8)。

こうした構成は、従来ARMが得意としてきたコントローラー系の用途にはまるで適さない。逆に言えば、ARM v7では「Cortex-A/R/M」という3種類にアーキテクチャーを分け、それぞれに適した内部構成を採用することで、こうした構成が可能になったと言える。

ちなみに、この時にはまだ設計目標が示されただけで、実際の性能値などは示されなかった。2006年5月に開催された半導体関連イベント「Spring Processor Forum 2006」(SPF2006)では、ARMから実装例が発表されている(図9)。

- TSMC 90nm Gプロセス、1.0V駆動、2000DMIPS、0.58mW/MHz

- TSMC 65nm LPプロセス、1.2V駆動、1875DMIPS、0.5~0.55mW/MHz

- TSMC 65nm LPプロセス、1.1V駆動、1550DMIPS、0.34~0.4mW/MHz

さすがに同じ90nm Gプロセスを使うと、ARM1176J(F)-Sより消費電力が増えているが、65nmのLPプロセスで低電圧駆動させた場合、多くても310mW程度で済んでいる。それでいて性能は2倍になっているのだから、これは大きな進歩と言える。

この連載の記事

-

第770回

PC

キーボードとマウスをつなぐDINおよびPS/2コネクター 消え去ったI/F史 -

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ - この連載の一覧へ