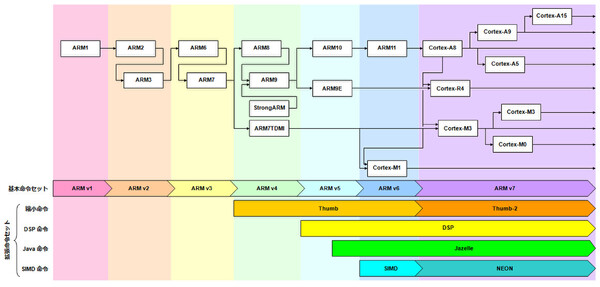

ARM編第1回の前回で、おおまかなロードマップと製品の特徴は説明した。今回はもう少し細かく、アーキテクチャーの特徴などを説明していきたい。

といっても、ARMプロセッサーは何しろ種類が多い。そこで話をアプリケーションプロセッサーに限り、「ARM11」以降の話をしよう。

大きな改良とともに登場した ARM11

ARM11のベースとなる「ARM v6」アーキテクチャーが発表されたのは、2001年10月に開催された半導体業界イベント「Micro Processor Forum(MPF) 2001」でのことだ。当時の発表資料を見ると、ARM v5からの改善事項として以下の項目が挙げられている。

- キャッシュアーキテクチャーの改善

- SIMDの搭載

- 命令セットの改善

- SoC/マルチプロセッサー向けの改良

(同期メカニズムの搭載や新メモリーモデルのサポート)

具体的にはバイエンディアンのサポート※1や、「Unaligned Memory Access」の対応※2、1次キャッシュのサポート(ARM v5までキャッシュは1階層)、「VMSA(Virtual Memory System Architecture) v6」の搭載などの項目が並んでいる。

※1 それまでのARMはリトルエンディアンのみサポートしていたが、ARM v6からLリトルエンディアン/ビッグエンディアンの両方をサポートするようになった。

※2 ARM v5までは、メモリーアクセスは必ず4byte単位だったが、v6から2/1byte単位のアクセスも可能になった。

もっとも、2001年に発表されたのはあくまでも命令セットであるARM v6のみ。これを実装した最初のARM11コアである「ARM1136J-S」「ARM1136JF-S」の発表は、2002年10月に開催された「MPF2002」となった。

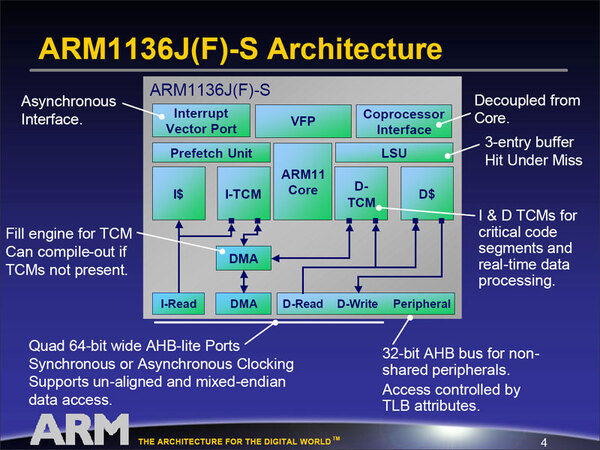

ARM1136J-Sの内部構造は、図1のようになっている。CPUコアについては後述するが、その両側に命令/データの1次キャッシュと「TCM」がそれぞれ配されている。TCMとは「Tightly Coupled Memory」の略で、簡単に言えばCPUから極めて高速(ほぼ1次キャッシュと同じレイテンシ/バンド幅)でアクセスできるメモリーである。

「それならキャッシュでいいだろう?」という声が聞こえそうだが、キャッシュの場合、基本的にはハードウェアが勝手にFill/Retireをしてしまう(プリフェッチ命令などを使い、ある程度明示的に制御することも不可能ではないが)。そのため、例えばリアルタイム制御における割り込みハンドラのような、「キャッシュミスを起こすとそれだけで処理がタイムアウトする」ような性能に厳しい処理の場合、キャッシュに頼らずに確実にプログラムのロード(フェッチ)ができる方法が必要になる。

こうしたケースで役に立つのが、キャッシュ並みに高速なメモリーである。サイズそのものは小さいから(構成によるが、後述の例では16KB)、大きな処理ロジックを載せるには不向きだが、割り込み処理ルーチンくらいなら楽に搭載できる。これはデータ側のTCMも同じだ。例えば周辺機器と高速にデータ入出力を行なう必要がある場合、通常のメモリー経由では余分にレイテンシが掛かってしまう(メモリーから一度キャッシュを経由するため)。しかし、外部からTCMにそのままDMA転送でアクセスすれば、キャッシュを経由しない分少ないレイテンシーでアクセスできるわけだ。

TCMに類するものは、例えばMIPS系であれば「ScratchPad」と呼ばれるメモリーが利用できる。PowerPC系にはTCM/ScratchPadはないものの、「Cache Stashing」(CPU外部から直接キャッシュの内容を書き換える)という機構を持ったものがあり、これでData TCMの代替が可能である。

こうした特長は、当時はまだARM11がアプリケーションプロセッサーよりもコントローラー的な用途に使われるケースが多いと、想定されていたことに起因すると考えていいだろう。ほかにも、図1左上には割り込みコントローラ(Interrupt Vector Port)、右上にはコプロセッサー用のインターフェースが用意されている。単にCPUだけではなく、さまざまなコプロセッサーと組み合わせて使うことを当初から想定してあるあたりは、単なるアプリケーションプロセッサーとは大分異なる。

もっとも、搭載するのはあくまでもキャッシュとTCMだけで、肝心のメモリーやメモリーコントローラーを内蔵しないあたりは、コントローラーというよりもプロセッサー向けの構造といえる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ