最近x86とArmに続く第3の勢力として、RISC-V(リスクファイブ)の名前を聞くことが多くなった。RISC-Vの場合、x86とArmと異なるのはさまざまなベンダーがさまざまなコアを用意していることで、まだ現状はIPを販売しているレベルの企業の方が多いが、チップの提供を開始しているメーカーも出始めている。

イメージとしては、1980年代末~90年代のx86市場を考えれば良い。インテルとAMD以外にCyrix/IDT/TI/IBM/NexGenなど多数のメーカーが、独自の実装に基づくx86プロセッサーを市場投入していた時代に近い。

もちろんいろいろ異なる点もあるのだが、2010年代前半はプロセッサーといえばx86とArm、それにPowerPC/POWERといった程度がせいぜいだったのに、なぜ2010年代後半から急速にRISC-Vが盛り上がったのか、という一連の流れを数回に分けて説明しよう。

目的は超省電力プロセッサーの開発

RISC-Vの生みの親は、米UCB(University of California, Berkeley:カリフォルニア大学バークレー校)のKrste Asanović教授である。Asanović教授はもともと2010年から“Resiliency for Extreme Energy Efficiency”と呼ばれる研究プロジェクトを2018年まで行なっていた。

このプロジェクトは、UCBのASPIREというプロジェクトの一部を成すもので、要するに超低消費電力なプロセッサーを構築するための回路技術やアーキテクチャーを構築するという目的に立っていた。

この目的のためにRAVEN-1と呼ばれるプロセッサーを自分たちで設計・製造しようとしたのだが、ここで問題になったのが「ではどんな命令セットを採用すべきか」だったのだ。

このプロジェクトの成果は2016年に“A RISC-V Vector Processor With Simultaneous-Switching Switched-Capacitor DC–DC Converters in 28 nm FDSOI”として論文がJSSC(IEEE Journal of Solid-State Circuits)に採択されているが、RAVEN-1上で複数のベンチマークを稼働させ、倍精度浮動小数点演算で26.2GFlops/Wの効率を実現したことを発表している。

つまり、特定の処理だけを行なうような専用回路ではなく、複数のベンチマークを稼働させられるような汎用プロセッサーでなければならない。汎用プロセッサーである以上、なんらかの命令セットは必要である。

ではここで必要な命令セットの特徴はなにか? というのが以下になる。

(1) 必要十分な命令セットであること

(2) 命令セットを自由にカスタマイズできること

(3) 無駄なコストが掛からないこと

そもそもこれは研究プロジェクトであり、しかも超省電力プロセッサーが目的である。したがって、(1)にあるように必要最小限の命令だけを実装するようにしたい。不要な命令をサポートするのは、そのサポートの手間だけでなくマイクロコードのエリアサイズも余分にかかる(そもそもマイクロコードを使うのが消費電力低減のためにはよろしくない)。

場合によってはデコードだけでなく実行ユニットの側にも余分な回路が必要になるかもしれない。そうしたものは、単にエリアサイズが大型化するだけでなく、リーク電流に起因する静的な消費電力増につながる。あくまでも研究に必要な機能だけが欲しいわけだ。

そして研究プロジェクトであるから、(2)で挙げたように実装の中で命令セットを変更したりしたい、あるいはより効率的に実行できる命令を見つけたりすることは当然あり得るし、その場合は命令セットそのものに手を入れたいだろう。そうした自由度がないと研究プロジェクトには向かない。

(3)も言わずもがなである。研究費は無尽蔵ではないからだ。もちろん大学向けに無償ライセンスが提供される場合もあるので、必ずライセンス料が掛かるとは限らないのだが。

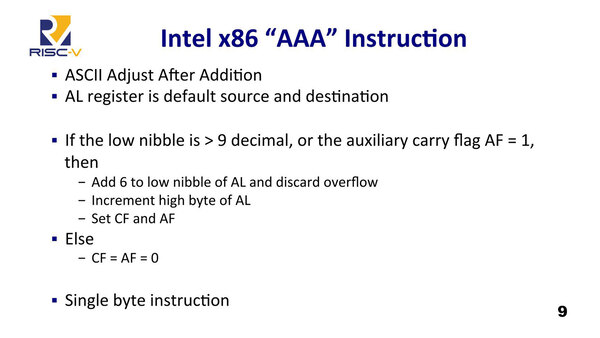

こうした条件で考えると、実は既存の命令セットはほとんどが不適切である。x86はライセンス供与されていないし、(1)や(2)に関しても適当とは言えない。例えばx86のAAA命令は下の画像のようになっている。

x86のAAA命令。x64命令はどんどん複雑怪奇化している。連載731回にも書いたが、頭にPrefixを付けることでいくらでも拡張できてしまう関係で、対応しなければならない命令数が多すぎるという問題がある

これを実装するのは大変である。商用プロセッサーであればこのくらいの実装は普通なのだが、研究プロジェクトでこの調子で命令を実装していくのは大変に困難である。これはArmも同じである。命令が複雑怪奇すぎる上、アーキテクチャーライセンスを受ければ実装は可能だが、(1)と(2)は不可能である。

Armは厳密に命令セットを定義しており、命令セットのすべての実装を要求してくるし、勝手に命令セットを変更することはできない。Armのアーキテクチャーライセンスは、命令セットを実装する回路を自由に作れる権利であり、命令セットそのものの改変は原則として不可能である。

原則、というのはMCU向けのArmv8-Mに関してはカスタム命令拡張をサポートして、ユーザーが若干命令を追加できるようになったためだ。もっともこれは既存の命令を改変できるわけではないし、アプリケーションプロセッサー向けのArmv8-Aに関してはまだ提供されていない。あと研究機関向けの無償ライセンスは存在するが、アーキテクチャーライセンスはこの枠外であり、なので(3)にも引っかかる。

この連載の記事

-

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 - この連載の一覧へ